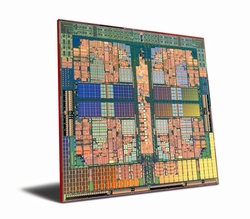

De eerder gemelde vertraging van de Phenom 9700 (2,4 GHz) wordt toch niet alleen veroorzaakt door de problemen met de overgang naar 65 nm. De site Golem en ook de Inquirer weten te melden dat er een diepere oorzaak aan ten grondslag ligt, die tevens een aantal andere processors van AMD raakt.

Tijdens de lancering van het Spider platform op 14 november jl. verraste product manager Dave Everitt vriend en vijand met een verklaring waarin gesteld werd dat de Phenom processor een fout heeft die onder bepaalde omstandigheden en pas bij 2,4 Ghz optreedt. Twee dagen later bleek uit een interview met dezelfde product manager echter dat alle processoren met de K10 architectuur (dus ook de Barcelona processors) last kunnen hebben van dezelfde bug.

De fout zit in de TLB (Translation Lookaside Buffer) van de L3 cache. Bij moderne CPU's die werken met virtueel geheugen dient de TLB voor het omzetten van virtuele in fysieke geheugenadressen. Bij bepaalde vormen van belasting van de vier cores zorgde de fout in de TLB ervoor dat het hele systeem kon vastlopen. Een workaround van AMD was om via een BIOS aanpassing de L3-TLB uit te schakelen. Dit ging echter wel ten koste van ruwweg 10% van de rekensnelheid.

Ondanks het feit dat de bug volgens AMD slechts onder speciale condities kan optreden heeft AMD er nu toch voor gekozen om het probleem voor de 9700 met een nieuwe stepping (B3) op te gaan lossen. Dit heeft echter wel tot gevolg dat de huidige steppings (B2) van de 2,4 GHz processor teruggeroepen worden uit de retailkanalen en de introductie van het snelste model opnieuw verder vertraging oploopt. Al met al loopt de introductie van de langverwachte Phenom X4 nu wel uit op een lichte deceptie voor AMD.