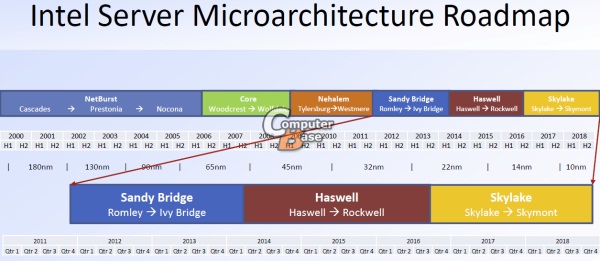

Met de tick-tock strategie probeert Intel het ene jaar een kleiner productieprocedé voor meer transistors uit te brengen (tick), om het jaar daarop met een nieuwe architectuur (tock) te komen die deze optimaal kan benutten. Feit is dat het voor de chipbakker steeds lastiger wordt om zich hieraan te houden, nu de fysieke grenzen in zicht komen. Een nieuwe roadmap voor het serversegment toont de plannen voor komende jaren.

De roadmap houdt zich primair bezig met de platforms en de architectuur die toegepast zal worden in serverprocessors, en die over het algemeen slechts met marginale aanpassingen ook gebruikt wordt voor high-end desktopchips. Te zien zijn onder andere een aantal bekende namen die de afgelopen jaren de revue passeerden. Op dit moment bevinden we ons vlak voor de introductie van Sandy Bridge, dat halverwege het vierde kwartaal gelanceerd zal worden, vermoedelijk in november. Het bijbehorende platform staat ook wel bekend onder de codenaam 'Romley'.

De volgende stap wordt de 'Ivy Bridge tick' die de Sandy Bridge architectuur naar kleinere 22 nm transistors brengt. Vanaf begin 2014 zal vervolgens de volgende tock plaatsvinden in de vorm van 'Haswell'. Voor het gemak lijkt Intel vanaf dat moment het high-end platform dezelfde codenaam te gaan geven als de architectuur. Zoals tijdens Computex al bekend werd, zal Haswell ook de basis gaan vormen voor de Ultrabook-visie van de fabrikant. Het serversegment loopt doorgaans echter wat achter op de consumenten-markt, wat betekent de eerste Haswell-gebaseerde producten al in 2013 zullen verschijnen.

De Haswell architectuur zal onder de codenaam 'Rockwell' de overstap maken naar een kleiner productie-procedé, dat naar verwachting 14 nm zal zijn. Momenteel werkt Intel al aan de nodige fabs die gebruik zullen maken van deze nieuwe procestechnologie. Halverwege de tweede helft van 2016 zal er weer een tock plaatsvinden als 'Skylake' geboren wordt. De daaropvolgende tick resulteert in 'Skymont' op 10 nm transistors. Vóór die tijd zullen bestaande productiefaciliteiten een upgrade krijgen om deze bijzonder kleine transistors te kunnen fabriceren.

De platforms zullen gepaard gaan met diverse andere evoluties van bestaande technologieën. Zo wordt verwacht dat de PCI-Express standaard voorlopig een integraal onderdeel zal blijven. Op dit moment zijn de eerste PCI-Express 3.0 producten reeds gelanceerd, op tijd voor het high-end Romley platform. Geschat wordt dat met Skylake versie 4.0 van de standaard het levenslicht zal zien, hoewel de voornaamste details ervan al eind dit jaar vastgelegd zullen worden.

Afbeelding is klikbaar en afkomstig van ComputerBase

Bron: ComputerBase