Op het Amerikaanse International Electron Devices Meeting gaat IBM meer vertellen over de werking van zijn langverwachte nieuwe 3D-chips voor de servermarkt. Het driedimensionale aspect betreft 45 nm-CPU's die vergezeld gaan worden van DRAM-geheugen en transceivers die zowel signalen kunnen versturen als ontvangen. Door de hoogte in te gaan, zouden fabrikanten met een 3D-ontwerp stroom gaan besparen en sneller kunnen werken.

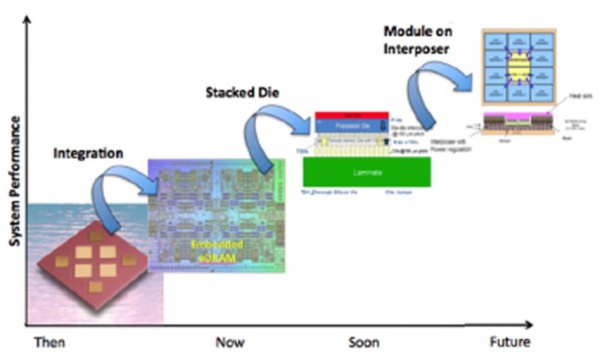

Het bedrijf geeft een (moeilijk leesbare) grafiek vrij waarbij het haar plannen voor de toekomst uiteenzet. Zo is te zien dat IBM nu werkt aan complete gestapelde dies, als vervanging van toegevoegde materialen op losse chips. Daarnaast wil het ook elektrische verbindingen opzetten tussen de zogenoemde 'stacks', waarbij er varianten gaan komen met stapels die naar elkaar toe of van elkaar af gericht zijn. De metaallagen voor het 22 nm productieproces heeft het al klaar, deze zouden geoptimaliseerd zijn om de elektronische verbindingen in aan te brengen.

Een analist van IBM noemt de ontwikkeling belangrijk om de wet van Moore in stand te kunnen houden, die zegt dat het aantal transistoren in chips elke twee jaar verdubbelt. De andere bevindingen die Subraman S. Iyer heeft gedaan, zijn nog niet openbaar gemaakt.

Bron: EETimes