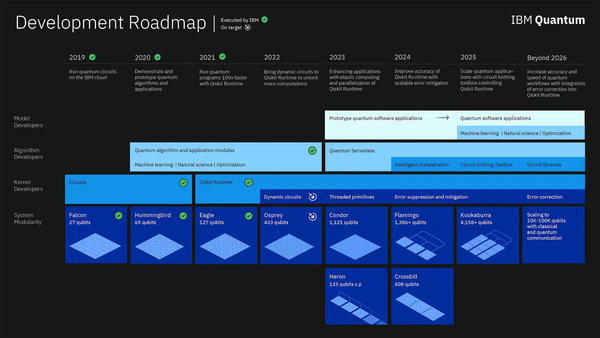

IBM deelde in 2020 al plannen om in 2023 de Condor-processor met 1.121 qubits gereed te hebben. Voor de twee jaar daarna doet het techbedrijf daar nog een schepje bovenop met respectievelijk 1.386 en 4.158 qubits in 2024 en 2025. Daarmee wordt in drie jaar bijna een vertienvoudiging behaald, dit jaar moet de Osprey met 433 qubits nog onthuld worden.

Tot 2023 wordt een monolithisch ontwerp gebruikt. Doordat het opschalen van deze dies moeilijk is stapt IBM daarna over op chiplets. Volgend jaar moet Heron met 133 qubits als prototype uitgebracht worden. Deze communiceert dankzij een ingebouwde controller over een universele bus met andere Heron-processors. De resultaten worden uiteindelijk door een klassieke cpu samengevoegd.

In 2024 moet Crossbill met 408 qubits geproduceerd worden. Deze bestaat uit drie chips op één carrier, waardoor er geen interconnect benodigd is. Dit moet uitvloeien in de Flamingo, die bestaat uit meerdere chips op een drager voor in totaal 462 qubits.

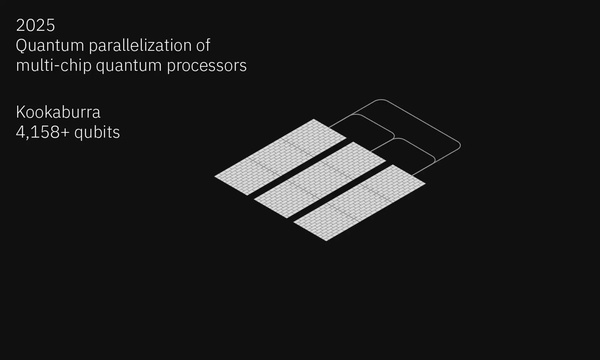

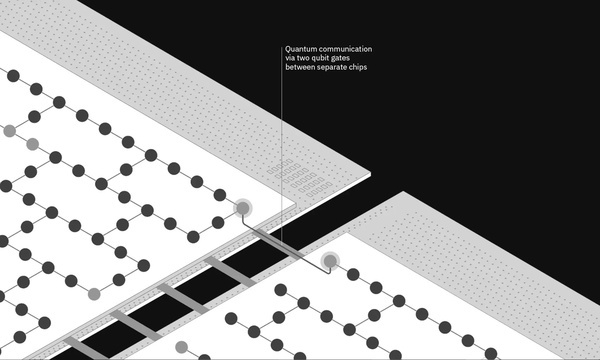

Minimaal drie van deze processors moeten onderling verbonden kunnen worden met de Quantum Communication Link. Deze neemt de conversie van qubit naar bits weg, wat complexere berekeningen op meerdere chips mogelijk maakt. Het nadeel is echter dat de kwaliteit van de qubits en dus van de resultaten hieronder lijdt. In 2025 moet dan de Kookaburra met 1.386 qubits uitkomen, die met twee andere processors tot 4.158 quantumbits in een systeem mogelijk maakt.

Vanaf Flamingo in 2024 wil IBM betere foutreductie en -onderdrukking introduceren. Vanaf 2026 volgt foutcorrectie, waarmee een van de grootste vraagstukken in quantum computing gedeeltelijk opgelost kan worden. Door de inherente instabiliteit van quantumdeeltjes kunnen de resultaten onnauwkeurig zijn, wat erg moeilijk te voorspellen en corrigeren is.

Uiteindelijk zouden er tien- tot honderdduizend qubits in een systeem met quantuminterconnects samengevoegd moeten worden met klassieke verbindingen en conventionele cpu's. Een systeem zou dan gestructureerd zijn als een flinke serverkast, met processors op basis van chiplets op een moederbord dat voor de onderlinge verbindingen zorgt.

Bron: heise