Zen 3: focus op efficiëntie per core

Het mag duidelijk zijn dat AMD van plan is om de Zen 3-cpu's snel op de markt te brengen. Er duikt nog altijd een grote hoeveelheid informatie op, genoeg om door de bomen het bos niet meer te zien. Tijd voor een overzichtje dus.

In mei ging het gerucht dat AMD de Ryzen 4000-chips voor het AM4-platform ging maken op TSMC's 5nm+-node, in plaats van op 7 nanometer. AMD heeft dit zelf ontkracht op een investeerdersbijeenkomst. De chips worden gewoon gemaakt op TSMC's 7nm-proces en ze moeten gewoon nog vóór het eind van dit jaar verschijnen.

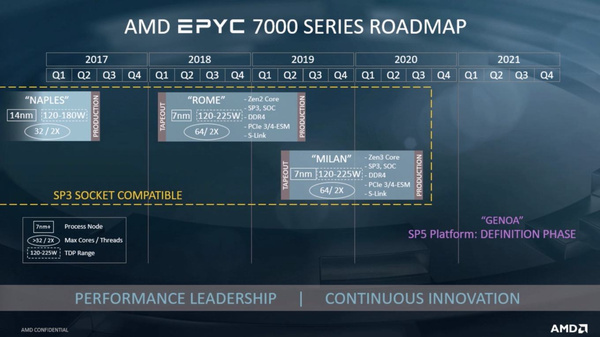

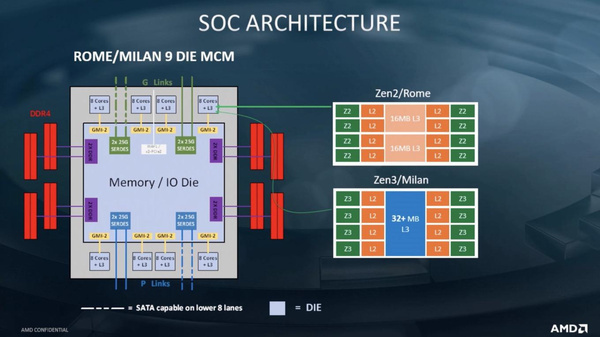

Naast nieuwe Ryzen-chips wordt ook Epyc vernieuwd met de Milan-generatie. Deze chips zouden evenveel cores krijgen als de Rome-cpu's. Ze moeten het dus vooral hebben van verbeteringen in de architectuur, net als wat we verwachten van de Zen 3-consumentenproducten. De verbeteringen zouden significant zijn, er wordt gesproken over een gemiddelde instructies-per-klok-toename van 10 tot 15%. Onderdeel hiervan zou zijn dat de L3-cache nu gedeeld kan worden door alle acht cores in een chiplet, in plaats van dat de cache pool is opgesplitst in twee delen per chiplet.

Bij het eerste Zen 3-nieuws doken er wilde geruchten op over 4 threads per cpu-core voor de nieuwe Epyc-generatie, een techniek die bijvoorbeeld IBM toepast in zijn Power-chips. De nieuwe Power10-chips kunnen zelfs tot 8 threads per core aan. Door een kern vaker aan te spreken bevindt hij zich minder in rusttoestand, wat net als bij simultaneous multi threading zorgt voor betere prestaties. Het rode team heeft inmiddels al op een conferentie door laten schemeren dat een dergelijk hoog aantal threads per core niet geïntegreerd zal worden.