Hoe ziet de toekomst eruit?

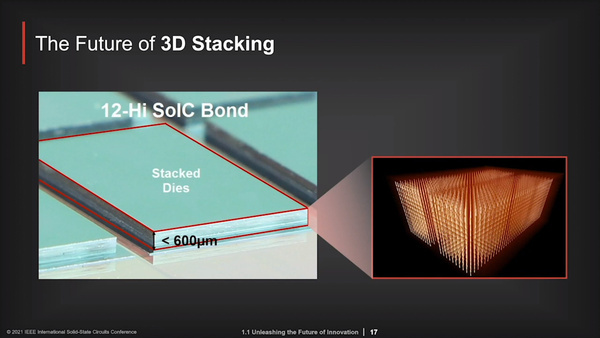

Om de chips van de toekomst nóg sneller en efficiënter te kunnen maken, worden allerlei belovende technologieën bekeken. Een voorbeeld hiervan is 3D-stacking. Zo moet het mogelijk zijn om met behulp van low temperature-bonding tot wel 12 dies op elkaar te stapelen, met een totale hoogte van minder dan 600 micrometer. Voor een dergelijk systeem is het van cruciaal belang om de i/o-count tussen de verschillende chips te verhogen. Dit moet zorgen voor een zo hoog mogelijke bandbreedte, terwijl het energieverbruik relatief beperkt blijft.

Een chip met 12 gestapelde dies, met een röntgenfoto rechts

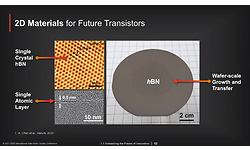

2D en 1D

Naast 3D-stacking kan het gebruik van laag-dimensionale materialen een oplossing bieden. Hoewel dergelijke technieken nog niet zijn toegepast in de chipindustrie, zijn er de afgelopen jaren veel doorbraken bereikt. Zo is men erin geslaagd om een zeshoekig kristal te vervaardigen uit boornitride, op de schaal van een wafer (afbeelding linksonder). Dit materiaal kan bij lage temperaturen worden overbracht naar substraten. Vervolgens moet het mogelijk zijn om logica- en geheugenlagen aan te brengen in drie dimensies.

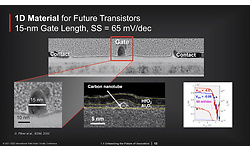

Om nog een stapje verder te gaan, bekijkt TSMC ook de mogelijke toepassingen van 1D-carbon nanotubes (koolstofnanobuizen). Om transitoren met carbon nanotubes te laten werken is er echter nood aan een diëlektricum dat transitoren met een korte gate length ondersteunt. Tijdens de International Electron Devices Meeting (IEDM) in december zijn de resultaten van een onderzoek onthuld, waarin wordt aangetoond dat het mogelijk moet zijn om carbon nanotube-transistors te produceren met een poortlengte van 10 nm.

Vele kleintjes maken een grote

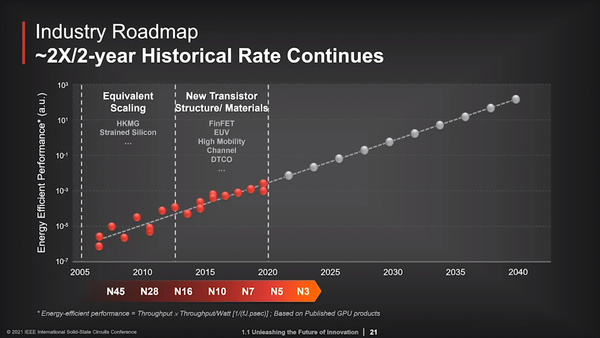

Uiteindelijk zal een combinatie van verscheidene technieken moeten zorgen voor de prestatieverbeteringen van de chips van morgen. Dr. Liu benadrukt tenslotte de nood aan en nauwe samenwerking tussen alle spelers in de halfgeleiderindustrie, van leveranciers en ingenieurs tot de academische onderzoeksgemeenschap. Alleen zo zal men in staat zijn om aan hetzelfde tempo vooruitgang te boeken op het vlak van efficiëntie en prestaties.

Volgens het Taiwanese bedrijf zal zijn 3nm-proces soortgelijke prestatie- en efficiëntieverbeteringen bieden als N5.