Inleiding - N3

Afgelopen week ging de International Solid-State Circuits Conference 2021 van start (ISSCC). In de loop van dit virtuele evenement heeft dr. Mark Liu, bestuurder bij TSMC, een presentatie gegeven over de vooruitgang van het aankomende 3nm-proces van het bedrijf. Daarnaast kwamen enkele technieken aan bod, die moeten bijdragen aan de prestatie- en efficiëntieverbeteringen van toekomstige procedés.

De volledige presentatie kun je hier bekijken.

Dr. Mark Liu, chairman bij TSMC

3 nanometer

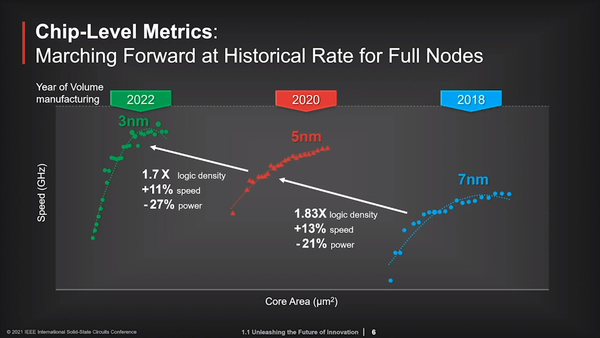

Liu bevestigt nogmaals dat de ontwikkeling van N3 op schema ligt. De risk-productie moet dit jaar nog van start gaan. Als alles verloopt zoals gepland, gaat de massaproductie van start in 2022. Zoals eerder is bekendgemaakt heeft N3 een 1,7 keer hogere transistordichtheid dan N5, of 58% van het chipoppervlak bij hetzelfde aantal transistors. De 3nm-node moet tot 11% sneller zijn bij hetzelfde energieverbruik, of tot 27% minder verbruiken bij dezelfde kloksnelheden.

TSMC heeft tot dusver ongeveer 1,8 miljard chips geproduceerd op zijn 7nm-proces.

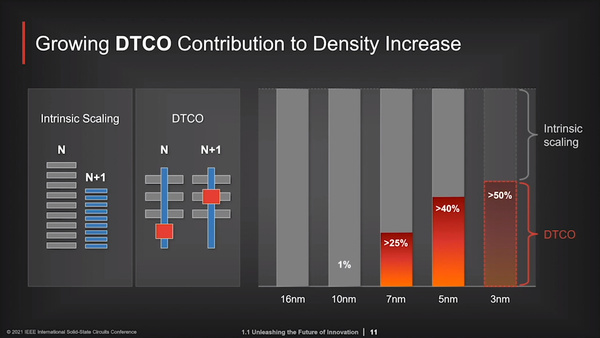

Vervolgens toont de TSMC-chairman aan hoe Design Technology Co-Optimization (DTCO) steeds meer bijdraagt aan het verhogen van de transistordichtheid van elke nieuwe node. DTCO is mogelijk dankzij het gebruik van nieuwe technieken zoals single diffusion breaks, fin-depopulation en verschillende zelfuitlijnende functies. Hierdoor geven eigenschappen zoals de contacted gate pitch en minimum metal pitch geen accuraat beeld meer van de transistordichtheid van een procedé.