Onder de motorkap: I/O is king

Epyc is gebaseerd op de Zen-processorarchitectuur die we al kennen van de Ryzen-processors. Een uitgebreide beschrijving van de architectuur is te vinden op pagina 8 tot en met 11 van onze AMD Ryzen 7 1800X review. In dit artikel zullen we niet verder ingaan op de specifieke eigenschappen van de architectuur, maar wel op wat de Epyc-uitvoering bijzonder maakt. Dat is primair de manier waarop AMD de vier chips binnen de CPU combineert en het platform van een gigantische hoeveelheid I/O-kanalen voorziet.

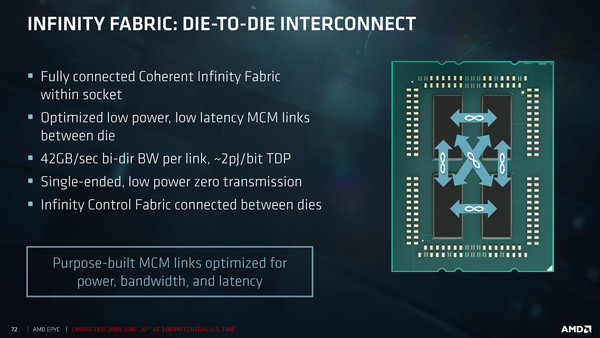

Om de vier chips binnen de processor met elkaar te laten communiceren, gebruikt AMD het Infinity Fabric protocol dat men binnen de Zen-architectuur (en overigens ook binnen de Vega GPU) ook gebruikt om chiponderdelen te laten communiceren. Iedere chip binnen de processor is met een link direct verbonden met elk van de andere drie chips, waardoor er dus in totaal zes die-to-die Infinity Fabric interconnects zijn. Die verbindingen zijn geheel coherent, wat betekent dat wanneer dezelfde data in de caches van meerdere chips zit, deze bij een bewerking daarop door één van de cores direct in alle chips wordt geïnvalideerd. De interconnects tussen de die's bieden een bidirectionele doorvoersnelheid van 42,6 GB/sec. De totale inter-die bandbreedte binnen de Epyc processors bedraagt zo 6 x 42,6 = 255,6 GB/s.

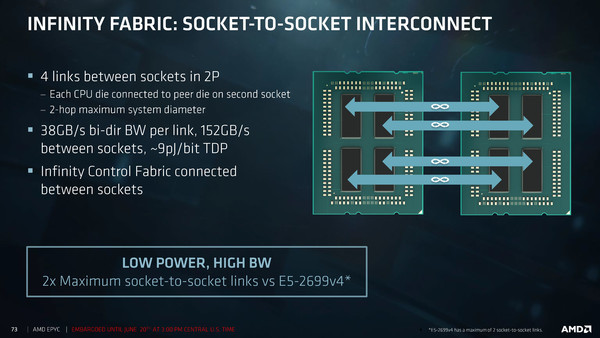

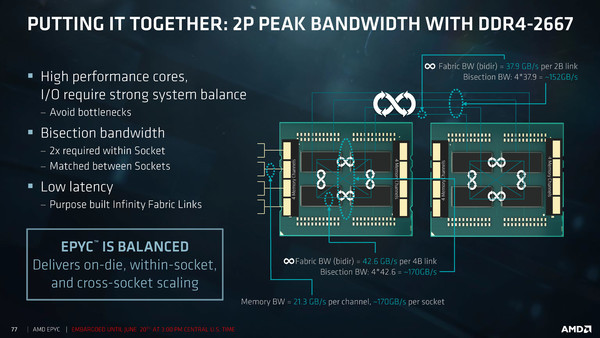

In dual-socket configuratie veranderen er wat zaken. Zoals op de vorige pagina geschreven bieden de Epyc processors 128 PCI-Express 3.0 lanes. In een 2P-configuratie worden 64 lanes per CPU echter gebruikt voor onderlinge communicatie. Hiervoor wordt echter het Infinity Fabric protocol gebruikt, dus niet PCI-Express. In feite wordt dus een ander signaal naar dezelfde pinnen in de sockets geloodst. In zo'n dual-socket configuratie is het niet langer zo dat binnen één CPU iedere chip een directe link heeft met iedere ander chip; de kruislingse verbindingen verdwijnen. Juist die Infinity Fabric verbindingen wordt via de socket naar buiten, naar de andere CPU geloodst, waarbij elk van de vier chips in verbinding staat met z'n evenknie in de tweede processor. De Infinity Fabric verbinding tussen twee sockets werkt op 37,9 GB/s bi-directioneel. Dankzij vier van die verbindingen is de totale communicatie tussen beide CPU's dus 4 x 37,9 = 151,6 GB/s. In een 2P-configuratie is de inter-die communicatie binnen een enkele CPU beperkt tot 4 x 42,6 = 170,4 GB/s.

Wanneer voorzien van DDR4-2667 modules op alle acht geheugenkanalen, is de totale geheugenbandbreedte per CPU circa 170 GB/s (21,3 GB/s per kanaal). AMD geeft aan dat wanneer de inter-chip- en geheugenbandbreedtes vergeleken worden, dat geconcludeerd mag worden dat het platform volledig gebalanceerd is. Daar is op dit vlak inderdaad weinig op aan te merken, maar hier moeten we wel direct bij vermelden dat over latency's niet wordt gesproken in de officiële slides, behalve de opmerking "low latency". Het is vooralsnog onbekend wat de latency is als een core data nodig heeft uit de L3-cache van een andere chip in dezelfde CPU of uit de L3-cache van een chip uit een tweede processor. Bij echt multi-threaded workloads kan dat in potentie een bottleneck zijn. Zoals we op de vorige pagina al schreven, AMD toont in haar slides enkel Spec CPU-benchmarks, waarbij het zo is dat bij deze benchmarks dezelfde workload simpelweg meerdere keren naast elkaar wordt gedraaid en er dus geen onderlinge communicatie is. Hoe bijvoorbeeld een multi-threaded database server of een HPC-workload zal draaien is dus nog afwachten.

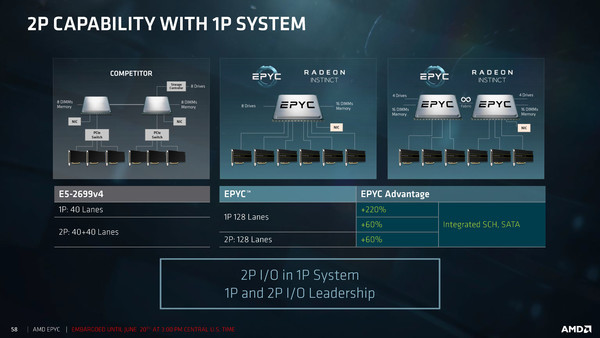

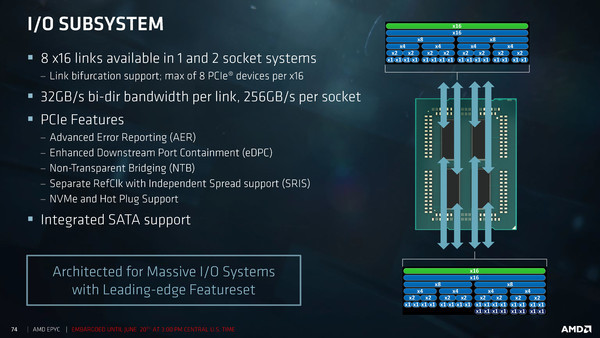

Waar AMD zonder meer Intel voorbij streeft is de hoeveelheid beschikbare PCI-Express lanes; zowel in een single- als een dual-socket configuratie zoals geschreven 128 lanes. Bij de huidige Intel generatie (Broadwell) is dat beperkt tot 40 lanes, wat met PCIe multiplexers wel weer opgehoogd kan worden, maar dat verhoogt de kosten van een server weer.

Het grote aantal PCIe-lanes maakt dat Epyc-systemen eenvoudig vele GPU's kunnen aansturen. AMD prijst Epyc dan ook niet voor niets aan als ideale basis voor haar eigen, later dit jaar verschijnende Radeon Instinct GPU's voor machine learning applicaties. Het zijn natuurlijk niet enkel GPU's die aan de PCIe lanes gekoppeld kunnen worden; het platform is ook geschikt voor grote aantallen PCI-Express gebaseerde SSD's.

De Epyc-processors zijn zogenaamde SoC's en vereisen dus geen extra chipset. Eén belangrijke opmerking hierbij: hoewel zaken als USB 3.0 en SATA native worden ondersteund, maken ze fysiek gebruik van dezelfde uitgangspinnen op de CPU. Dat betekent dat dergelijke functionaliteit ten koste gaat van het beschikbare aantal PCI-Express lanes. Wanneer een serverfabrikant bijvoorbeeld besluit om 6x USB 3.0 en 6x SATA te implementeren, zijn er dus 12 PCIe lanes minder beschikbaar, al blijven er nog altijd veel over in vergelijking met het huidige Intel Broadwell-EP platform.