De Peripheral Component Interconnect Special Interest Group heeft tijdens zijn jaarlijkse ontwikkelaarsconferentie in Santa Clara (Californië, VS) versie 0.3 van de pcie 7.0-specificatie gedeeld. Hiermee wordt aangetoond dat de eerste draft-versie vervolledigd is en is goedgekeurd door de leden van de organisatie, wat wil zeggen dat de standaard naar verwachting zal klaar zijn in 2025.

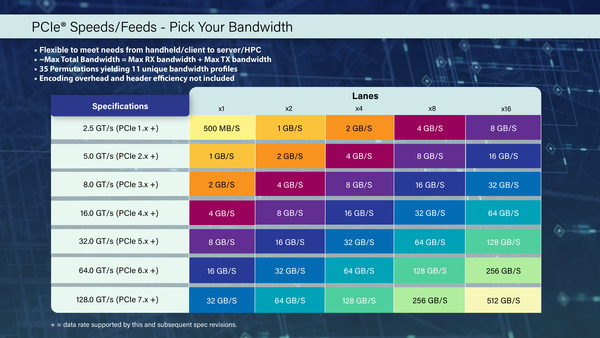

Na de officiële vaststelling van versie 6.0 is de PCI-SIG snel aan de slag gegaan met zijn opvolger. Bijna precies een jaar geleden zijn de eerste details van pcie 7.0 naar boven gekomen. Zoals gewoonlijk wordt er van een verdubbeling gesproken ten opzichte van zijn voorganger, wat wil zeggen dat versie 7 een datarate van 128 GT/s moet mogelijk maken. Dit levert een bi-directionele bandbreedte van maximaal 512 GB/s op bij een x16-slot (zonder encoding-overhead).

De groepering heeft eerder al bevestigd dat pcie 7.0 net zoals pcie 6.0 PAM4-signalering combineert met 1b/1b flit mode-codering. Men zal dus andere aspecten moeten bekijken om de verhoogde doorvoersnelheid te kunnen realiseren, waaronder de fysieke laag.

De PCI-SIG voorspelt dat de ontwikkeling van versie 1.0 van de specificatie zal worden afgerond in 2025. De eerste apparaten met deze technologie zullen echter pas in de loop van 2027 worden uitgebracht.

Bronnen: PCI-SIG, AnandTech, Tom's Hardware