Tiger Lake met Willow Cove

Nog voor de kerst wil Intel laptops met zijn Tiger Lake-processors in de handen van consumenten krijgen. Tiger Lake maakt deel uit van de 11de generatie Core-processors en is de directe opvolger van Ice Lake. Vorige week kondigde Intel reeds aan dat het op 2 september een livestream zal uitzenden om de processors officieel aan te kondigen, maar op zijn Architecture Day gaf Intel alvast de nodige technische details.

Willow Cove: mega-cache en hogere klokfrequenties

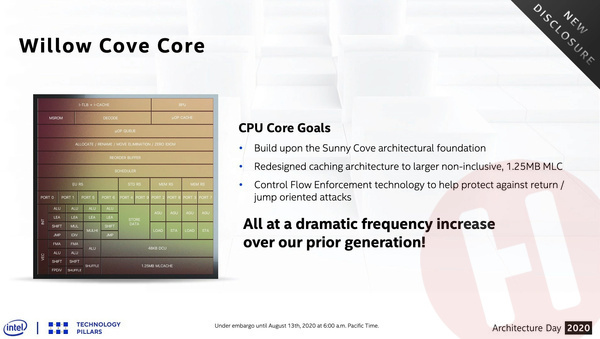

Tiger Lake wordt zoals gezegd geproduceerd op het nieuwe 10nm SuperFin-procedé, maar bevat daarnaast ook een nieuwe core. Willow Cove borduurt grotendeels door op de grote stap die met Sunny Cove werd gezet - die core bracht een ipc-verbetering van gemiddeld 18% met zich mee. De grootste veranderingen zijn een vernieuwde cachestructuur en voornamelijk véél hogere klokfrequenties dan de bestaande Ice Lake-chips.

De mid-level cache oftewel L2-cache werd bij Sunny Cove al vergroot van 256 kB per core naar 512 kB. Bij Willow Cove bevat elke kern echter een gigantisch blok van 1,25 MB L2-cache. Blijkbaar verwacht Intel daar veel van, want het sram-geheugen dat hiervoor wordt gebruikt neemt relatief veel die-oppervlak in beslag. Ter vergelijking: AMD's Zen 2-architectuur heeft 512 kB per core aan L2-cache.

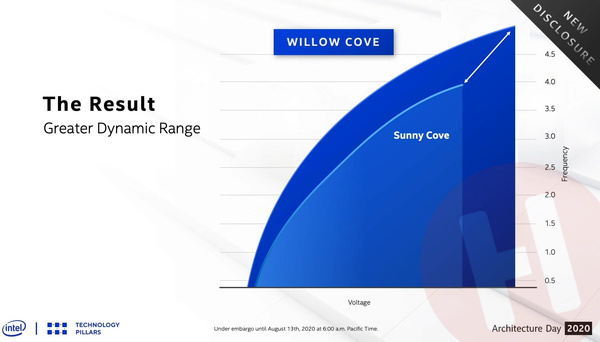

Primair dankzij het verbeterde productieproces moet Willow Cove op veel hogere klokfrequenties kunnen werken dan zijn voorganger. Tot nu toe was de beperkte frequentieschaling een duidelijke achilleshiel van Intels 10nm-procedé, maar uit een grafiek die Intel toonde blijkt dat Willow Cove in staat moet zijn om de 5 GHz aan te tikken, waar de snelste Ice Lake-chips met Sunny Cove niet hoger kunnen turbo'en dan rond de 4 GHz. Tegelijkertijd moet Willow Cove bij letterlijk elke willekeurige klokfrequentie afkunnen met een lagere spanning dan Sunny Cove, en daarmee dus ook een hogere efficiëntie behalen.

Overigens is Willow Cove ook voorzien van Intels nieuwste Control-Flow Enforcement Technology, een mooie naam voor de combinatie van indirect branch tracking en shadow stack. Deze technologieën moeten hardwarematige bescherming bieden tegen respectievelijk jump/call-oriented en return-oriented aanvallen. Een toekomstige versie van Windows 10 zal hier ondersteuning voor bieden.

Anderhalf keer grotere 'Xe-LP' geïntegreerde gpu

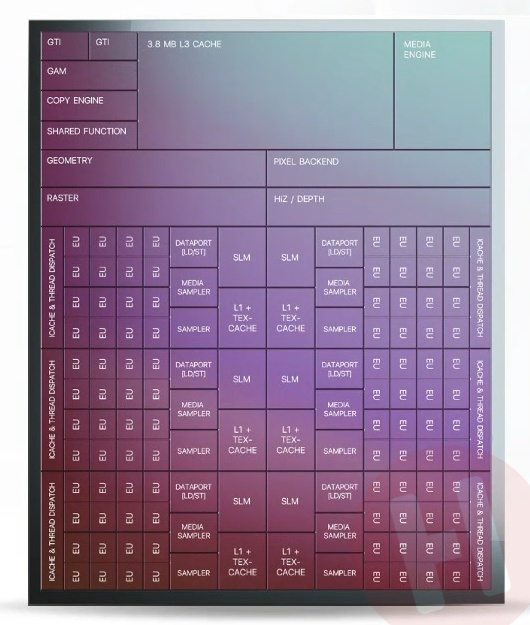

Naast een viertal Willow Cove-cores, die relatief gezien maar een klein deel van de Tiger Lake-chip beslaan, beschikt de nieuwe processor ook over een grotere geïntegreerde videochip. In zijn snelste uitvoering heeft de gpu 96 execution units, waar dat bij Ice Lake ophield bij 64 stuks. De XeLP-architectuur die aan de basis van de nieuwe geïntegreerde graphics staat, is in feite alweer de opvolger van de Gen11-architectuur die bij Ice Lake werd geïntroduceerd en moet voor een fors verbeterde performance-per-watt zorgen. Later in dit artikel gaan we nog wat dieper in op Intels plannen op grafisch gebied.

Dubbele ringbus, geheugen en I/O

Alle onderdelen van de Tiger Lake-chip (waaronder overigens ook 12 MB L3-cache) moeten natuurlijk met elkaar kunnen communiceren. Daarvoor gebruikt Intel al sinds jaar en dag de zogenaamde ringbus-architectuur, als het ware een ringweg die langs onder meer de processorcores, caches en gpu komt. Het belangrijkste nadeel hiervan is dat een processor met meer 'stops' - meer cores dus - te maken krijgt met steeds langere en bovendien minder voorspelbare interne latencies. Als remedie paste Intel in het verleden soms een dubbele ringbus toe bij processors met zeer veel cores, al gebruikt het daarvoor tegenwoordig een geavanceerdere mesh-structuur. Opvallend genoeg maakt Intel juist voor Tiger Lake, met 'slechts' vier cores, de overstap naar een dubbele ringstructuur. Vragen hierover wist Intel vooralsnog niet te beantwoorden.

Verder maakt Tiger Lake gebruik van een verbeterde geheugencontroller met ondersteuning voor LPDDR4X-4267 en DDR4-3200, met de mogelijkheid om toekomstige modellen ook te laten werken met DDR5-5400. Aan de i/o-kant heeft Intel thunderbolt 4 en usb 4 geïntegreerd met maximaal 40 Gb/s bandbreedte per poort, plus de mogelijkheid om het videosignaal van een losse videokaart uit te voeren via usb-c. De pci-express controller heeft een upgrade gekregen naar versie 4.0, al zou het aantal lanes en daarmee de totale bandbreedte variëren per model.

Een wafer met Intel Tiger Lake-processors