Roadmap: Alder Lake en packaging

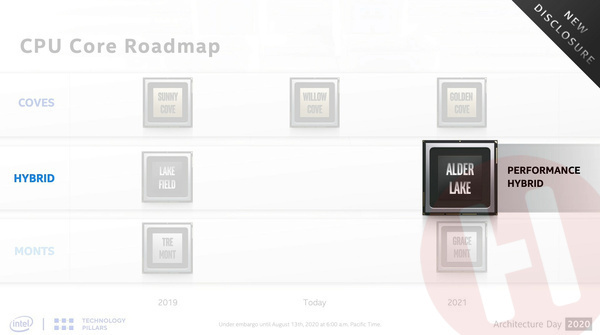

Onderdeel van de Architecture Day zijn natuurlijk ook de roadmaps voor de komende jaren. De roadmap voor de ontwikkeling van nieuwe processorkernen kenden we grotendeels al. Na Willow Cove komt Golden Cove, met als focuspunten hogere single-threaded prestaties, verbeterde AI-acceleratie, netwerk/5G performance en wederom nieuwe beveiligingstechnieken. De Atom-derivaat Tremont, beter bekend als Intels 'kleine core', krijgt volgend jaar tevens een opvolger in de vorm van Gracemont, met ipc en vector-prestaties als belangrijkste verbeteringen.

Intel is nog lang niet klaar met big.LITTLE

Een nieuwe aankondiging die Intel deed valt daar eigenlijk tussenin. Recent testten we de eerste laptop met een Intel Lakefield-processor, waarin één snelle Sunny Cove-core werd gecombineerd met vier kleine Tremont-cores. Het doel daarvan was het (standby-)energieverbruik zeer laag houden voor een lange accuduur, terwijl de laptop dankzij de enkele grote core toch responsief aanvoelt. Intel bevestigt nu dat het in 2021 met een Alder Lake komt, naar eigen zeggen de eerste 'performance hybrid'.

Zelf wilde Intel weinig anders kwijt dan dat Alder Lake bestaat en volgend jaar verschijnt, maar uit het geruchtencircuit wordt duidelijk wat Intel bedoelt met een 'performance hybrid'. Er komen namelijk tal van combinaties tussen maximaal acht grote cores (Golden Cove) en maximaal acht kleine cores (Gracemont). Voor de desktop zul je bijvoorbeeld kunnen kiezen voor een 8+8-configuratie, maar ook voor bijvoorbeeld 8+2, 8+0, 6+6 en 6+4. Om de grotere chips te huisvesten komt er een nieuwe, vermoedelijk rechthoekige socket 1700. Geruchten als ddr5- en pci-e 5.0-ondersteuning lijken realistisch, met het oog op wat we verder al weten van de toegepaste cores.

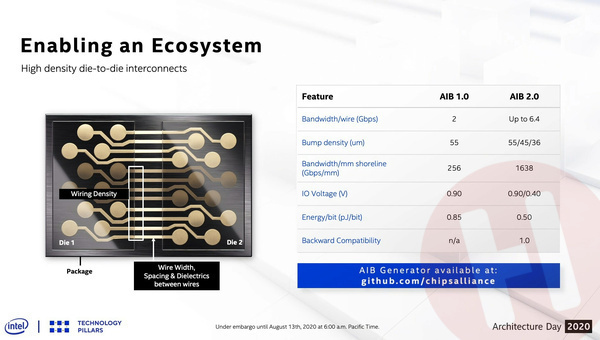

Standaard voor die-to-die interfaces

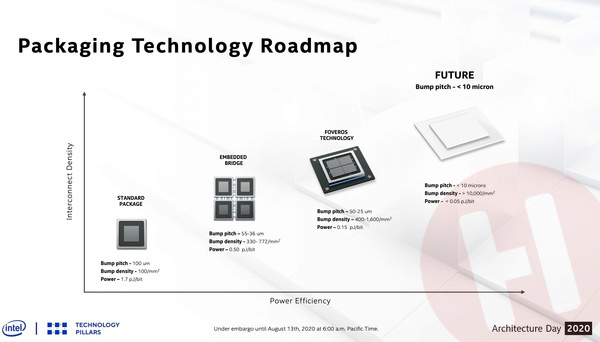

Om steeds diversere chips te kunnen bouwen - denk aan diverse procedés van verschillende fabrikanten door elkaar - timmert Intel ook hard aan de weg op het gebied van nieuwe packaging-methoden. Eerder ontwikkelde het al embedded bridge (emib), waarmee onder meer de Intel-cpu en Radeon-gpu in Kaby Lake-G aan elkaar werden geknoopt. Voor dergelijke die-to-die interfaces maakte Intel vorig jaar reeds de Advanced Interface Bus-standaard beschikbaar, die chiplets met elkaar verbinden net zo eenvoudig moet maken als hoe interfaces als pci-express en ddr op een pc-moederbord met elkaar praten. AIB 2.0 moet de bandbreedte ruim verdrievoudigen ten opzichte van de eerste versie en tevens mogelijkheden bieden om met kleinere bumps te werken. De totale hoeveelheid energie die nodig is per overgedragen bit zou dalen van 0,85 pJ naar 0,50 pJ.

Naast deze '2,5D'-technieken zagen we in de eerder genoemde Lakefield-processor ook de eerste volwaardige '3D'-oplossing, namelijk Foveros. Verschillende chiplets en een dram-chips werden in die processor niet naast elkaar geplaatst, maar op elkaar gestapeld. Ter vergelijking: waar emib een bump pitch van minimaal 36 micrometer mogelijk maakt met 0,50 pJ/bit, schaalt Foveros tot 25 μm en 0,15 pJ/bit.

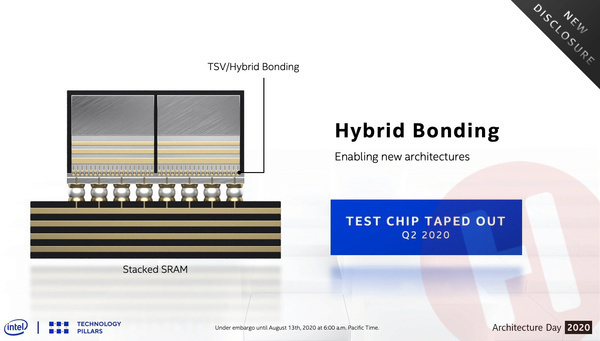

Om een volgende stap te kunnen zetten, werkt Intel aan Hybrid Bonding, een verticale interconnect met een veel hogere dichtheid. Hiervoor worden kleinere en simpelere circuits ingezet, met een lager stroomverbruik als gevolg. De eerste testchip is in het tweede kwartaal van dit jaar werkend uit de fabriek komen rollen, heeft een bump pitch van 10 μm en verbruikt 0,05 pJ/bit.

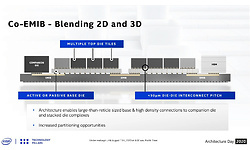

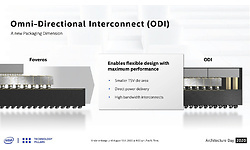

Daarnaast heeft Intel diverse technieken in ontwikkeling om bovenstaande methoden te combineren in één product. Zo werkt het aan co-emib, waarbij 3D-stacks onderling, met geheugen of met een ander die zijn verbonden via emib. Omni-directional interconnect (ODI) moet op lange termijn een mogelijkheid toevoegen aan Foveros om onder meer de power-delivery naar de hoger gelegen chips direct vanuit het base-die te doen, om zo ruimte van through-silicon via's door lager gelegen chips heen te besparen.