Inleiding

Ongeveer een week geleden publiceerden we een uitgebreide preview van de Intel Sandy Bridge processors, die begin volgend jaar op de markt moeten komen. Tijdens het Intel Developer Forum deze week, waar Hardware.Info aanwezig is, zijn er meer details over de nieuwe architectuur van deze chips bekend geworden. In dit artikel nemen we de nieuwste informatie met je door. De informatie die al in de genoemde preview vermeld stond, wordt in dit artikel niet herhaald. Mocht je de eerdere preview niet gelezen hebben, raden we je aan dat alsnog te doen.

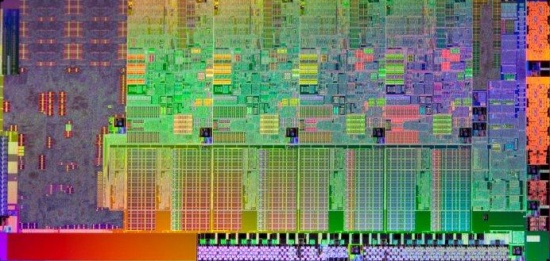

Die-shot van de Sandy Bridge chip die begin volgend jaar op de markt komt.

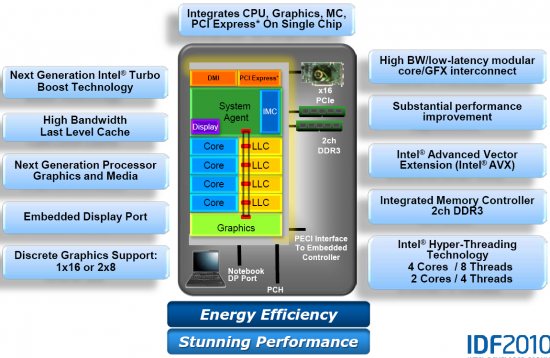

Blokschema

Tijdens de verschillende briefings over Sandy Bridge heeft Intel officieel het blokschema van de processor bekend gemaakt, zoals te zien op onderstaande afbeelding. Het was al bekend dat de eerste Sandy Bridge processors een viertal cores krijgen, een dual-channel DDR3-geheugencontroller, een geïntegreerde GPU en verder een geïntegreerde PCI-Express controller. Op de afbeelding zien we hoe de verschillende onderdelen met elkaar verbonden zijn.

Wat in het blokschema direct opvalt is dat de verschillende onderdelen van de chip op elkaar gestapeld lijken te zijn. Onderin zit de GPU, daarbovenop de vier cores (elk rechtstreeks verbonden met een kwart van de totale hoeveelheid gedeelde L3-cache) en daar bovenop de overige onderdelen als de system agent (het onderdeel dat al het interne verkeer binnen de chip regelt), de geheugencontroller, etc. Deze opbouw is niet toevallig: Intel heeft zich bij Sandy Bridge tot doel gesteld om de processor zo modulair mogelijk te maken. Om een goedkopere dual-core versie te maken, kan men relatief eenvoudig twee van de blokken met een core en een stuk L3-cache wegnemen en de rest weer aan elkaar plakken. Op dezelfde manier zijn relatief eenvoudig varianten van de chip zonder geïntegreerde GPU te maken, zonder dat er een geheel nieuw chipontwerp nodig is. Maar het werkt ook de andere kant op: een variant met zes, acht of meer cores maken is met deze modulaire insteek ook veel eenvoudiger dan bij oudere chipontwerpen, waar alle functionaliteit met elkaar verweven is.

Over het modulair opbouwen van processors wordt al lang gesproken en uit het blokschema mogen we afleiden dat Intel dit bij de Sandy Bridge generatie voor het eerst zeer ook zeer goed in de praktijk brengt.

Een belangrijke vernieuwing binnen de Sandby Bridge architectuur is de interface waarmee alle onderdelen van de site met elkaar communiceren. Intel heeft gekozen voor een ringbus, waar alle cores, alle blokken L3-cache, de geïntegreerde GPU en de system agent mee zijn verbonden. Zo'n ringbus kun je nog het beste vergelijken met een ring snelweg rond een stad (bijvoorbeeld de A10 bij Amsterdam) met meerdere op- en afritten. Wanneer je snel van de ene plek in de stad naar de andere wil, rij je naar de dichtstbijzijnde oprit, rij je daarna afhankelijk van wat het kortst is linksom of rechtsom naar de afrit die het dichtst bij je bestemming is en daarna ga je weer binnendoor. Het mooie van zo'n ring is dat je, net als bij de stad, zo veel mogelijk opstoppingen binnen de chip beperkt. Daarnaast werkt de ring ook mee aan de modulariteit van de chip: het weghalen of toevoegen van cores is ook simpelweg een kwestie van het weghalen of toevoegen van afritten op de ring.

De ringbus binnen Sandy Bridge werkt op een duizelingwekkende snelheid 96 Gigabit/s in beide richtingen.