Uitdagingen

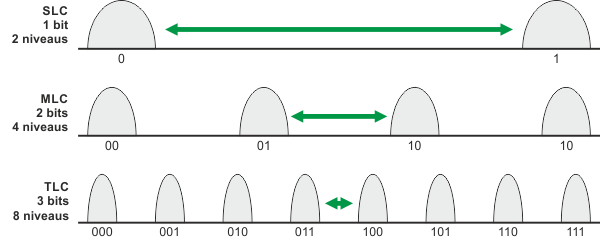

Het principe van het programmeren van flashgeheugen is altijd hetzelfde, maar er is wel verschil in hoeveel bits er in een cel kunnen worden opgeslagen. Bij single level cell-geheugen (SLC) is dat één bit: 0 of 1. Bij MLC is dat twee bits, wat vier waardes kunnen zijn: 00, 01, 10 of 11. Bij TLC ten slotte zijn dat drie bits, voor deze mogelijke waardes: 000, 001, 010, 011, 100, 101, 110 en 111. Elk van die bitwaardes wordt vertegenwoordigd door een (negatieve) elektrische lading, ofwel een hoeveelheid elektronen. Bij SLC zijn dus twee ladingsniveaus nodig (waarvan één 0 kan zijn), bij MLC zijn dat er al vier en bij TLC zelfs acht. Dat heeft twee belangrijke consequenties, die zwaarder gaan wegen naarmate het productieprocedé kleiner wordt.

In TLC-geheugen moet een cel acht verschillende ladingen kunnen bevatten.

Hoe fysiek groter de transistor, hoe groter de floating gate en hoe meer elektronen die kan opslaan, hoe eenvoudiger het is om in die hoeveelheid te variëren om meerdere niveaus aan te brengen. Hoe kleiner de transistor, hoe kleiner de floating gate, hoe minder elektronen erin passen, hoe moeilijker het is om meerdere goed van elkaar te onderscheiden ladingniveaus aan te brengen. Ook zal duidelijk zijn dat je bij MLC (en nog meer bij TLC) minder speelruimte hebt voor voltagewisselingen. Immers, met dezelfde maximale hoeveelheid elektronen moet je bij TLC acht bitwaardes kunnen representeren, versus twee bij SLC.

Het probleem van de continue productieprocedéverkleining is zoals gezegd tweeledig. In de eerste plaats zorgt het proces waarmee een cel wordt voorzien van een lading voor slijtage. Het hoge voltage waarmee NAND geprogrammeerd moet worden, zorgt ervoor dat de isolatielagen (het ONO en het siliciumoxide) wegslijten, wat in de praktijk betekent dat ze hun isolerende eigenschappen verliezen. Daardoor kunnen elektronen uiteindelijk niet meer wegstromen uit de floating gate, of niet meer terugkeren naar het siliciumsubstraat. Dat zorgt voor een ongewenste verandering van het voltage in de cel en daarmee een foutief opgeslagen bitwaarde. Bij MLC en TLC, waarbij de voltages dichter op elkaar liggen, treedt dat effect significant sneller op – vandaar de lagere levensduur, cq. het kleinere aantal schrijfcycli dat deze typen flash aankunnen. Naarmate deze flashcellen kleiner worden, wordt het effect van slijtage groter: er is immers minder materiaal dat kan slijten.

Naast de slijtage vormt ook de miniaturisering zelf een uitdaging voor de werking. Het verkleinen van de omvang van een flash-cel zorgt ook voor een verkleining van de floating gate, die bij elke stap minder elektronen kan bevatten. Ter illustratie van de dimensies waarover we het hebben; het 15nm NAND-geheugen van Toshiba en Sandisk kan minder dan 20 elektronen per cel opslaan. Dat betekent in het geval van TLC, dat er minder dan 3 elektronen per voltageniveau beschikbaar zijn! Een handvol ontsnapte (weggelekte) elektronen betekent al dat de cel niet meer functioneert, ofwel verkeerde data bevat.

Daarnaast is ook de nabijheid van de cellen een factor. Zoals we al schreven is een essentieel onderdeel van de moderne mosfet in NAND-geheugen dat de control gate door middel van een capacitieve verbinding de floating gate kan beïnvloeden. Als de individuele transistors echter te dicht op elkaar komen te liggen, neemt het risico toe dat naburige cellen elkaar via zo’n capacitieve verbinding gaan storen. Die storing varieert met de spanning die er op een naburige cel staat, dus het is geen constante, waardoor het niet mogelijk is deze storing via een algoritme te compenseren. De enige oplossing is een hoger voltage gebruiken, om de capacitieve geleiding tussen control gate en floating gate tot stand te brengen, waardoor de elektronenstroom door het oxide gaat lopen.

Een simpele analogie is een ruimte waarin diverse mensen aan het spreken zijn. Zolang ze allemaal ver genoeg uit elkaar staan, is het niet lastig om te verstaan wat de persoon zegt bij wie je het dichtstbij staat. Hoe kleiner de ruimte wordt en hoe meer de sprekers dus op elkaar komen te staan, hoe lastiger het wordt om elk daarvan individueel te verstaan. Als ze dan ook nog eens steeds zachter gaan praten, gaat het verhaal helemaal verloren. Zo gaat het ook met NAND-flashgeheugen: hoe dichter de cellen op elkaar zitten, hoe meer ze elkaar beïnvloeden, dus hoe moeilijker het is om een cel uit te lezen of te beschrijven. Dat wordt verder bemoeilijkt door de afnemende omvang van de cel.

De halfgeleiderfabrikanten hebben al heel wat gedaan om deze effecten tegen te gaan, van zogenaamde luchtbarrières tussen de wordlines tegen interferentie tot high K metal gates in plaats van klassieke oxide-nitride-oxide diëlectricums (isolerende lagen), maar het einde is nu echt in zicht. Om de Wet van Moore toch te kunnen blijven volgen en dus de kosten van transistors te blijven reduceren, heeft Samsung een radicale innovatie gedaan: het is met NAND de diepte (of liever gezegd: de hoogte) in gegaan, met vertical-NAND. Hoe zit dat?

4 besproken producten

| Vergelijk | Product | Prijs | |

|---|---|---|---|

|

Samsung 850 Pro 1TB

|

Niet verkrijgbaar | |

|

Samsung 850 Pro 128GB

|

Niet verkrijgbaar | |

|

Samsung 850 Pro 256GB

|

Niet verkrijgbaar | |

|

Samsung 850 Pro 512GB

|

Niet verkrijgbaar |