Geheugen: HBM2 en geheugen wordt cache

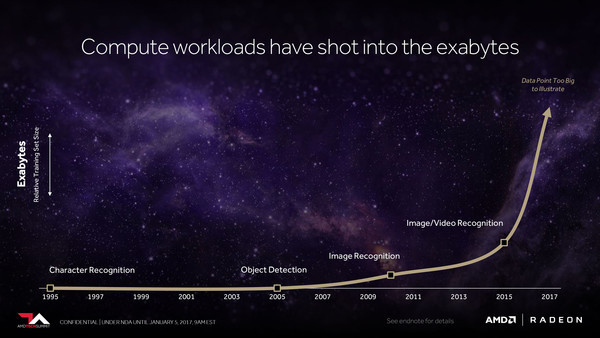

We schreven op de vorige pagina al dat Vega veel geschikter is voor grote datasets. Volgens AMD is dat goed voor games, maar vooral ook voor andere doeleinden. AMD geeft aan dat de installatiegrootte van moderne games sinds een aantal jaren exponentieel stijgt. Veel van die data is graphics-gerelateerd, bijvoorbeeld meer en gedetailleerdere textures. Het probleem van veel data is bij zogenaamde compute workloads nog veel groter; de datasets bij machine learning applicaties kunnen tot in de exabytes lopen. Véél meer dus dan de paar gigabyte die je in het lokale geheugen van de videokaart zelf kunt opslaan.

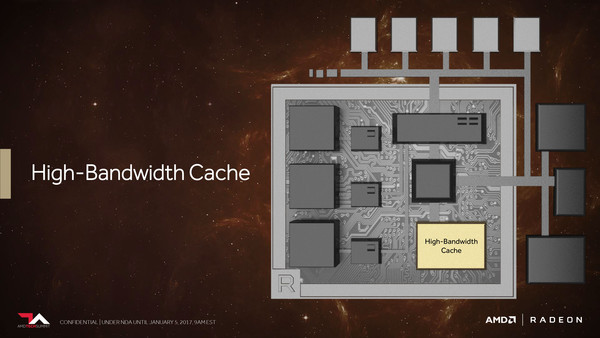

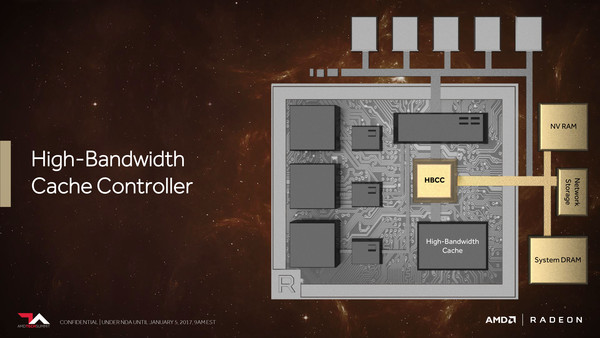

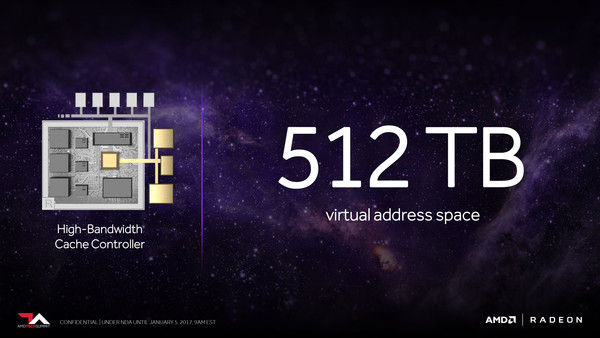

Dit alles vergt een frisse blik op de manier waarop geheugen door de GPU wordt behandeld. Bij Vega neemt AMD een radicale stap, niet zo zeer technisch, als wel qua naamgeving. Het geheugen dat rechtstreeks op de videokaart is gesoldeerd noemt men niet langer geheugen maar cache. Om die reden is de geheugencontroller in de GPU omgedoopt tot high band cache controller. Dit alles omdat men het geheugen op de videokaart in principe ziet als snelle cache voor de potentieel in omvang veel grotere hoeveelheid data die elders in het systeem staat, in het globale RAM-geheugen, op een SSD, op een netwerklocatie, of waar dan ook. Gezien GPU's al een L1-, L2- en L3-cache hebben, zou je het geheugen dan kunnen opvatten als een soort L4-cache, al wordt die naamgeving niet gebruikt. De Vega-chips kunnen volgens AMD maximaal 512TB geheugen adresseren. Slimme algoritmes in de controller moeten ervoor zorgen dat de data die op ieder gegeven moment daadwerkelijk gebruikt wordt door de GPU ook daadwerkelijk in het lokale geheugen aanwezig is.

In principe betekent dit dat we in het Vega-tijdperk moeten gaan praten over videokaarten met bijvoorbeeld "8GB cache" in plaats van "8GB geheugen". Of dat ook écht gaat gebeuren valt te betwijfelen; verwarrend is het zeker. Zo verwarrend zelfs, dat de technici van AMD tijdens de Vega-prestatie meermaals de mist in gingen en een uitgebreide groepsdiscussie met journalisten uiteindelijk dusdanig ontspoorde dat op een gegeven echt even gepauzeerd moest worden om expliciet duidelijk te maken waar iedereen het nu exact over had.

Wat we eigenlijk wel al wisten, maar nu door AMD expliciet is bevestigd, is dat de geheugencontroller, herstel, cache-controller binnen Vega geschikt wordt voor HBM2, ofwel de tweede generatie van het High Bandwidth Memory dat men voor het eerst toepaste bij de Fiji-GPU van de Radeon R9 Fury (X). High Bandwidth Memory is extreem snel geheugen dat direct naast de GPU binnen dezelfde chipverpakking op een zogenaamde interposer wordt geplaatst. Door die directe koppeling zijn veel meer dataverbindingen mogelijk. Een uitgebreid achtergrond artikel over HBM lees je hier terug.

Bij de Radeon R9 Fury X werd de GPU omringd door vier zogenaamde HBM-stacks van elk 1 GB. Deze stacks bestonden weer uit vier lagen van elk 256 MB. Iedere stack staat via een 1024-bit bus in verbinding met de GPU, zodat je dus mag concluderen dat de Fiji GPU in totaal een 4096-bit geheugenbus heeft. De HBM-chips werkten op 500 MHz DDR snelheid, ofwel met 1 gigabit/s geheugensnelheid per pin. De totale geheugenbandbreedte is met de 4096-bit verbinding dus 4096 gigabit/s, ofwel 512 GB/s.

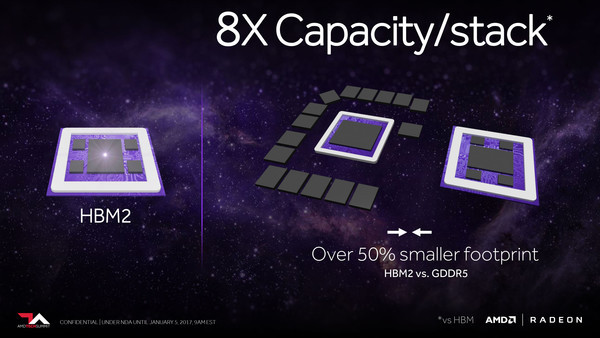

Bij HBM2 blijft de verbinding 1024-bit per stack, maar wordt de doorvoersnelheid verhoogd naar 1 GHz DDR, ofwel 2 gigabyte/s. Ook bij HBM2 zullen er vier stacks per GPU gekoppeld worden, waardoor de totale geheugenbandbreedte dus verdubbeld van 512 GB/s naar 1024 GB/s (ofwel 1 TB/s). Dat is meer dan twee keer zo snel als de 384-bit GDDR5X implementatie op de Nvidia GeForce GTX Titan X! De capaciteit per stack kan binnen de HBM2-standaard maximaal verachtvoudigd worden, enerzijds door 8 in plaats 4 lagen per stack mogelijk te maken en anderzijds door de maximale capaciteit per laag te verhogen van 256 MB naar 1 GB. Het maakt dat HBM2 het in principe mogelijk maakt om videokaarten met 32 GB geheugen cache uit te brengen. Dat zal echter niet direct het geval zijn; zowel Samsung als Hynix hebben afgelopen jaar aangekondigd in eerste instantie met HBM2 chips van 4GB per stack te komen. Dat zou dus betekenen dat de Vega-kaarten 4 x 4 = 16GB geheugen krijgen.