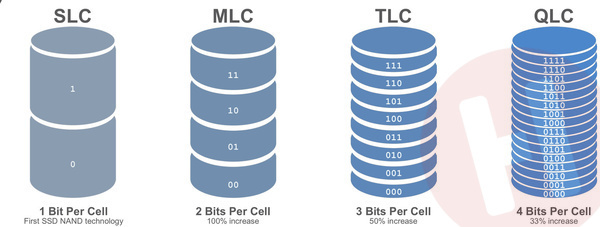

SLC, MLC, TLC en QLC

Eén van de drijvende krachten achter het steeds goedkoper worden van ssd’s is dat er in de loop der tijd technieken zijn ontwikkeld om meer dan één bit in een geheugencel op te slaan. De voordelen spreken voor zich: in dezelfde chip kun je hierdoor veel meer gegevens opslaan. Andersom geredeneerd heb je minder chips nodig om een bepaalde opslagcapaciteit te bereiken. Naast slc zijn mlc, tlc en qlc ontwikkeld, die respectievelijk staan voor multi-, triple- en quad level cell. De gangbare definitie van mlc is twee bits per geheugencel, al neemt met name Samsung daarmee een loopje door van (technisch enigszins correct) ‘3-bit mlc’ of ‘4-bit mlc’ te spreken. Hoe dan ook, de truc is om niet met twee spanningsniveaus te werken, maar met (veel) meer verschillende niveaus.

Bij mlc-geheugen is er dus sprake van vier spanningsniveaus, die zich laten vertalen in 00, 01, 10 of 11. Het eerste getal staat steeds voor de waarde van de eerste bit, het tweede getal voor die van de tweede bit. Het aantal niveaus verdubbelt bij elke toegevoegde bit: bij tlc zijn er acht spanningsniveaus, bij qlc zelfs zestien. Daar staat tegenover dat de stap van slc naar mlc nog dubbel zoveel capaciteit opleverde, terwijl dat bij mlc naar tlc nog maar 50% was en het toevoegen van een vierde bit zelfs maar 33% extra ruimte oplevert. Het opslaan van meer bits in dezelfde geheugencel kan echter niet straffeloos. Het verhogen van het aantal spanningsniveaus gaat gepaard met achteruitgang op twee belangrijke vlakken: de snelheid waarmee de geheugencel kan worden uitgelezen en beschreven (dat moet immers met meer precisie), en de levensduur van de cellen en daarmee van het complete flashgeheugen.

Vanuit slc-geheugen kan zeer snel worden gelezen: er hoeft alleen onderscheid te worden gemaakt tussen ‘vol’ of ‘leeg’. Hetzelfde geldt voor schrijfacties. Bij het uitlezen van qlc-geheugen moeten maar liefst zestien spanningsniveaus van elkaar worden onderscheiden. Dat gebeurt in de praktijk relatief inaccuraat, waardoor er geavanceerde foutcorrectie-algoritmes nodig zijn. Het uitvoeren daarvan kost steeds meer tijd en met name daarom is flashgeheugen bestaande uit meer bits per cel een stuk trager. Schrijfacties moeten eveneens met veel meer accuratesse worden uitgevoerd, wat doorgaans zelfs een nog grotere impact op de prestaties heeft dan bij lezen.

Nadelen

Om met name dit eerste nadeel van mlc-, tlc- en qlc-geheugen op te vangen, maakt vrijwel elke ssd gebruik van een zogenaamde slc-cache. Een deel van het flashgeheugen wordt daarbij aangestuurd als slc, dus in deze buffer wordt slechts één bit per cel opgeslagen. Een schrijfopdracht kan daardoor op ‘slc-snelheid’ worden verwerkt, om op een later moment te worden verplaatst naar het reguliere nand. Deze slc-buffer is tegenwoordig vaak dynamisch van formaat, wat betekent dat hij groter wordt als de ssd niet al te vol zit en er dus veel overtollig flashgeheugen is dat als slc-cache kan worden ingezet. Mede hierdoor kan een ssd echter wel langzamer worden als hij vol raakt.

Het tweede nadeel van het verhogen van het aantal bits dat in een geheugencel wordt opgeslagen, is dat de levensduur van het flashgeheugen wordt verkort. Flashgeheugen kan per definitie slechts een bepaald aantal keer worden beschreven, totdat het verschil tussen 0 en 1 door restlading niet meer goed is vast te stellen, waarover later meer. Hoe dan ook, bij nand met meer bits en dus meer spanningsniveaus, komt het moment dat twee naastliggende niveaus niet meer van elkaar kunnen worden onderscheiden steeds eerder. Er is immers een veel kleinere marge dan bij slc-geheugen.

Des te meer bits per cel, des te groter de opslagcapaciteit, maar ook met des te meer spanningsniveaus een ssd moet werken.

Een andere manier om flashgeheugen goedkoper te maken, is van oudsher het verkleinen van het productieproces. Dat kennen we van veel andere chips, zoals processors: meer transistors op dezelfde oppervlakte leidt tot lagere kosten, hogere prestaties en een toenemende efficiëntie. Bij de moeizame overstap naar productieprocessen van ordegrootte 20nm kwamen de geheugenfabrikanten echter tot de conclusie dat verdere verkleining een te grote impact zou hebben op de levensduur. Met het fysiek kleiner worden van geheugencellen neemt de hoeveelheid restlading waartegen ze bestand zijn immers in rap tempo af.

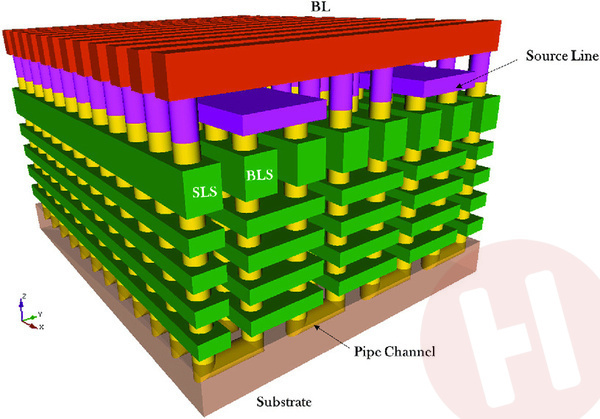

Sindsdien worden geheugencellen daarom niet of nauwelijks nog kleiner gemaakt om de dichtheid te verhogen, maar worden er meerdere lagen geheugencellen bovenop elkaar geplaatst. Dat vereiste significante investeringen in productiemethoden, en soms ook in gebruikte materialen, waarover we bij de introductie van 3d-nand uitgebreid schreven. Het leverde echter wel weer voldoende schalingsmogelijkheden op om in de voorzienbare toekomst steeds meer geheugencellen op dezelfde oppervlakte kwijt te kunnen.

Bij 3d-nand worden er meerdere lagen geheugencellen op elkaar geplaatst.

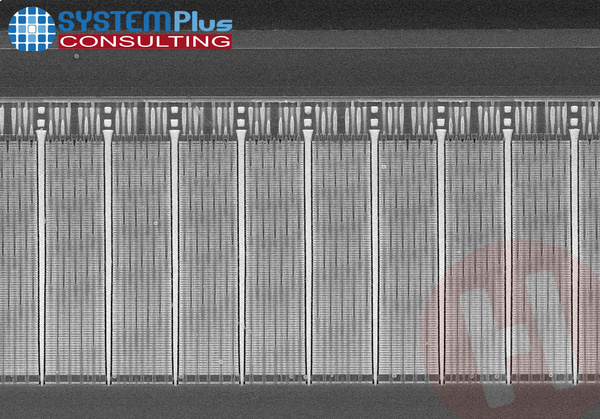

Een röntgenopname van een courante Samsung 3d-nand-chip met 92 lagen.