Verbetere geheugencontroller

AMD's sterke punt blijft natuurlijk de geïntegreerde geheugencontroller. Intel ziet dat inmiddels ook in en heeft zodoende aangekondigd haar eerstvolgende nieuwe architectuur (codenaam Nehalem) ook van een geïntegreerde geheugencontroller te voorzien.

De geheugencontroller in Barcelona is op een aantal punten flink verbeterd ten opzichte van de huidge Athlon 64 processors. Allereerst gaat Barcelona anders om met dual-channel geheugen. De bestaande Athlon 64 processors hebben een 128-bit geheugencontroller, wat betekent dat data telkens met 128 bits tegelijkertijd wordt gelezen of weggeschreven. Deze 128-bits worden verdeeld over twee geheugenkanalen, DDR(2)-modules accepteren immers 64 bits tegelijkertijd. Op dezelfde plekken binnen de geheugenbanken op de twee kanalen zit zodoende data die bij elkaar hoort. Bij Barcelona heeft men dit concept aangepast en de nieuwe CPU heeft zodoende niet één 128-bit, maar twee 64-bit controllers die elk één kanaal voor hun rekening neemt. De verschillende cores kunnen afzonderlijk gebruik maken van beide controllers, zodat bijvoorbeeld core 1 via de eerste geheugencontroller data wegschrijft in geheugenkanaal 1, terwijl core 3 via de tweede geheugencontroller data uitleest in geheugenkanaal 3. Dit kan naar verluidt wanneer er intensief gebruik wordt gemaakt van multi-tasking (of van virtualisatie) voor een flinke prestatiewinst zorgen.

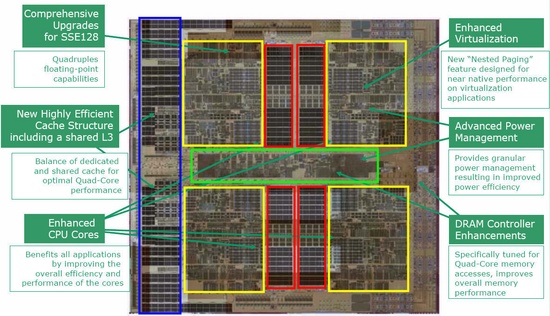

Die-shot van Barcelona.

Geel: 4x core, Rood: 4x 512 kB L2-cache,

Groen: geheugencontroller, Blauw: 2 MB gedelde L3-cache

Een andere belangrijke verbetering is een speciale buffer die schrijfacties opspaart en op een gegeven moment in één keer uitvoert. Schakelen tussen lees- en schrijfmodus bij geheugenmodules kost immers altijd een aantal kostbare kloktikken. Waar bestaande geheugencontrollers schrijfacties altijd direct uitvoeren wanneer ze arriveren, stopt de nieuwe geheugencontroller ze dus eerst in een buffer totdat op een later moment er een hele rits schrijfacties achter elkaar gedaan kunnen worden. In de tussentijd kunnen leesacties op de hoogste snelheid worden uitgevoerd, aangezien er nog maar zelden hoeft te worden gewacht op schakelen tussen lees- en schrijfmodus.

Uniek is dat AMD de geheugencontroller heeft voorzien van pre-fetchers. Deze voorspellen op basis van toegangspatronen welke data er in de nabije toekomst zal worden aangeroepen en lezen deze data alvast in naar een snelle buffer. Vanuit deze buffer kan de data wanneer nodig zeer snel naar één van de caches van de processor gekopieerd worden. Die caches zélf maken overigens ook weer gebruik van pre-fetchers, zoals dat ook in de architectuur van Intel het geval is. De extra pre-fetcher in de geheugencontroller kan er echter voor zorgen dat AMD in geheugenintensieve applicaties een extra streepje voor krijgt.

Als laatste is ook de interne bandbreedte van de geheugencontroller flink vergroot, ondermeer door het invoeren van grotere buffers. De geheugencontroller is op die manier al voorbereid op snellere geheugensoorten. Waar AMD's eerste generatie quad-core processors nog gewoon gebruik maken van DDR2 geheugen is de architectuur zodoende al voorbereid op DDR3 in toekomstige revisies.