Bulldozer

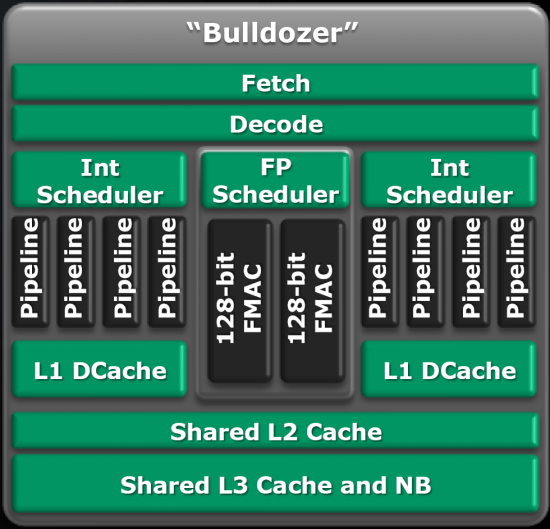

In de afbeelding op deze pagina zien we een blokdiagram van de Bulldozer kern, zoals AMD die een tijdje geleden wereldkundig heeft gemaakt. Wie geregeld naar het blokdiagram van een processor heeft gekeken, zal direct opvallen dat het ontwerp van Bulldozer licht afwijkend is. Heel algemeen bevat iedere processor-core een component die instructies binnenhaalt (fetch), een component die instructies decodeert om uitgevoerd te worden (decode) en een component (de scheduler) die instructies op een slimmere volgorde zet en daarna klaar zet om door verschillende rekeneenheden binnen de core verwerkt te worden. Een core van een Intel Nehalem processor bijvoorbeeld heeft een zestal execution units, waarvan drie geschikt voor berekeningen met integers (gehele getallen) of floating point (komma) getallen en drie geschikt voor bewerkingen met betrekking tot het geheugen (zie ook deze pagina).

Als het allemaal precies uitkomt (lees: de variatie in instructies van een programma is toevallig exact afgestemd op de verdeling van de execution units) kan een Nehalem core per klokslag zes uitgevoerde instructies afleveren. In de praktijk ligt het gemiddelde aantal instructies per seconde uiteraard wat lager. Om haar execution units zo gevuld mogelijk te houden, bedacht Intel in de tijd van de Pentium 4 een interessante technologie die binnen de Nehalem architectuur z’n rentree heeft gekregen: HyperThreading. Door deze technologie kunnen de instructie decoders en schedulers van Intel processors de instructies van twee programma’s of programma-threads tegelijkertijd verwerken. Het resultaat is dat veel zeker (bijna) alle zes de execution units van werk voorzien kunnen worden en dat het gemiddelde aantal per klokslag afgeronde instructies, en dus de algehele prestaties van de processor, toenemen. Om dit mogelijk te maken doen cores met HyperThreading zich ten opzichte van het besturingssysteem voor als zijnde tweede cores.

HyperThreading zorgt ervoor dat een processor veel beter is toegerust voor multi-threaded software, maar is hevig gepatenteerd door Intel. Bij Bulldozer voert AMD om hetzelfde doel te bereiken een andere truc door, die iets meer transistors kost, maar potentieel ook betere prestaties biedt: alle core onderdelen die bewerkingen met integers of geheugenadressen uitvoeren zijn dubbel uitgevoerd, zoals te zien in het blokschema: een Bulldozer core heeft twee losse integer schedulers, die elk een viertal pipelines aansturen. Beide integer blokken hebben de beschikking over een eigen stuk L1-cache. AMD heeft nog niet bekend gemaakt hoe de execution units van de vier integer pipelines werken: vermoedelijk zijn er twee geschikt voor getal berekeningen en twee voor geheugeninstructies. Door deze opzet is een enkele Bulldozer core voor integer en geheugenwerk in feite een dual-core. Het besturingssysteem zal zodoende Bulldozer cores ook als twee cores herkennen.

Het blokschema van de Bulldozer CPU-kern.