Hybrid Memory Cube

Geheugenfabrikanten Micron en Samsung werken zoals gezegd aan een vergelijkbare nieuwe geheugentechnologie, Hybrid Memory Cube (HMC). Hoewel bij HMC ook meerdere geheugenlagen worden gestapeld, is de filosofie bij deze technologie anders. Micron en Samsung willen juist geen geheugen maken dat direct op een CPU geplaatst kan worden of direct ernaast op dezelfde imposer. HMC, wat overigens (nog) geen Jedec-standaard is, moet een opvolger worden van DDR4-geheugen. Het moet initieel in servers en later ook in desktop PC’s in grote hoeveelheden aan een CPU gekoppeld kunnen worden. HMC-“chips”, die men cubes noemt, krijgen ook normale chipverpakkingen, net als DDR4-chips, en zouden dus in theorie ook prima op geheugenmodules geplaatst kunnen worden. Hierdoor hoeven Micron en Samsung, ondanks dat de technologie verandert, hun verdienmodel niet hoeven aanpassen: ze kunnen gewoon geheugenchips blijven verkopen. Het is wel mogelijk om deze cubes direct naast een CPU te plaatsen, maar dan op een eigen PCB. Micron noemt dat een near memory configuration.

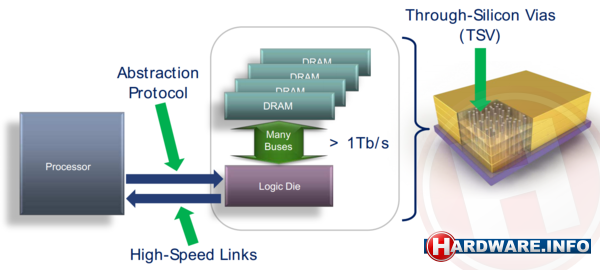

Ook bij HMC worden geheugenchips gestapeld, waarbij de DRAM-lagen vrijwel uitsluitend de geheugencellen bevatten en nagenoeg de complete aansturing in de onderste laag is verwerkt. De communicatie met de geheugencellen loopt ook bij HMC door de zogenaamde TSV’s.

Een groot verschil tussen HBM en HMC is dat HBM op een gelijkaardige manier als conventionele geheugenchips wordt aangestuurd, waardoor de geheugencontroller dus in de CPU of GPU moet zitten. Bij HMC zit de geheugencontroller in de geheugenchip zelf en die communiceert met de buitenwereld via een snel serieel protocol genaamd SerDes.

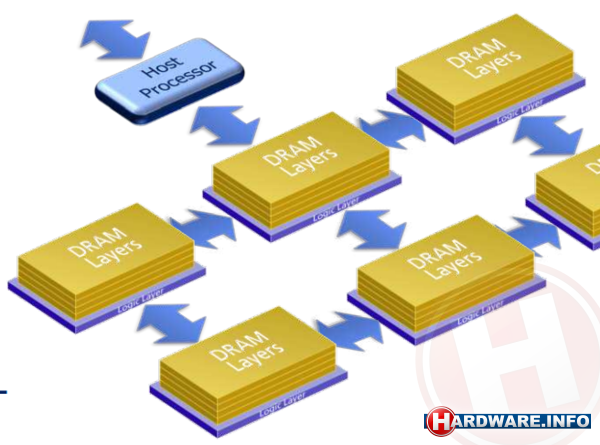

Iedere HMC-chip krijgt één of meerdere 8-lane of 16-lane full-duplex verbindingen met een snelheid van 10, 12,5 of 15 Gbps per lane. Gerekend met 10 Gbps voor de eerste generatie, zou de volledige bandbreedte van een 16-lane verbinding tussen HCM en GPU dus 40 gigabyte per seconde bedragen: 20 GB/s in beide richtingen. Door de cubes meerdere van deze SerDes links te geven – er wordt gesproken over 4 tot 8 – kunnen ze ook onderling met elkaar communiceren, om op die manier een groot aantal geheugenchips met één enkele CPU te verbinden. Op die manier kan in servers het aantal gigabyte per CPU flink vergroot worden.

De verbinding tussen CPU en GPU en HCM-chips vindt plaats via een gestandaardiseerd serieel protocol. De geheugencontroller zit nu in de geheugenchips zelf.

Door HCM-cubes meerdere links te geven, kunnen de chips aan elkaar gekoppeld worden om zo veel geheugen aan één CPU of GPU te koppelen.