Transistors bouwen

Op de wafer worden in diverse stappen miljarden transistors gebouwd en achteraf met elkaar verbonden. Het maken van die transistors gebeurt ruwweg in een vijftal fases. In eerste instantie wordt er extra elektrische isolatie aangebracht tussen de plekken waar de transistors worden geplaatst, zodat deze geen invloed op elkaar kunnen uitoefenen. Daarna wordt het silicium op de plekken waar de source, drain en gate komen voorzien van ionen. Daarna wordt de gate isolatie en daarna de gate aansluiting aangebracht. Zodra die op zijn plek zit worden source en drain opnieuw beschoten met ionen om op die manier de PNP of juist NPN karakteristiek te krijgen. Tenslotte wordt bovenop de transistor een isolatielaag aangebracht en worden metalen aansluitpunten voor source, gate en drain aangelegd.

De complete werkwijze van 32 stappen voor het maken van de transistors vind je achter deze link. Een aantal taken keert meermaals terug: fotolithografie, etsen en hem implanteren van ionen. Deze zaken nemen we stuk voor stuk met je door.

Lithografie

De transistors worden laag voor laag op de wafer gebouwd. Het is niet zo dat tijdens de productie op een ingenieuze wijze benodigde materialen op exact de plek waar ze benodigd zijn kunnen worden geplaatst. Zonder uitzondering wordt een nieuw materiaal over de gehele processors neergelegd en daarna waar het juist niet moet zitten weggehaald. Dat krijgen Intel en andere processorfabrikanten voor elkaar door een combinatie van fotolithografie en etsen.

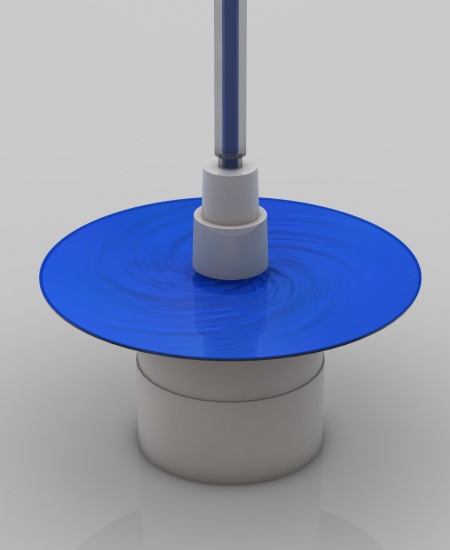

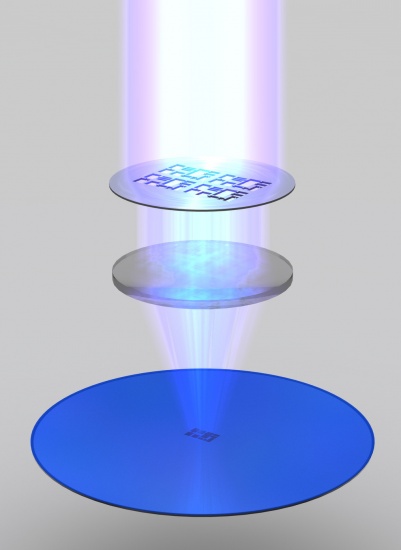

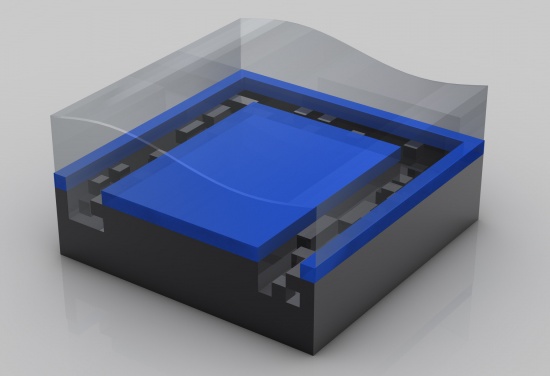

In onderstaande afbeeldingen zie je hoe dit proces in één van de eerste stappen van het productieproces wordt uitgevoerd. Allereerst zie je hoe een fotogevoelige vloeibare laag op de wafer wordt aangebracht. Tijdens dit proces draait de wafer rond, zodat de vloeistof op een gelijkmatige manier op de wafer terecht komt en er uiteindelijk een flinterdun laagje blijft zitten. Daarna wordt ultraviolet licht toegepast om de fotogevoelige laag op bepaalde plekken zachter te maken. Dit licht wordt door een masker met de indeling van de transistors geprojecteerd en daarna door een lens verkleind en naar de juiste plek op de wafer gestuurd. Dat klinkt simpeler dan het is: je moet je voorstellen dat dergelijker maskers voor een CPU met 700 miljoen transistors de complexiteit van de kaart van een wereldstad als Parijs heben, maar moeten worden geprojecteerd op een stukje van nog geen drie vierkante centimeter.

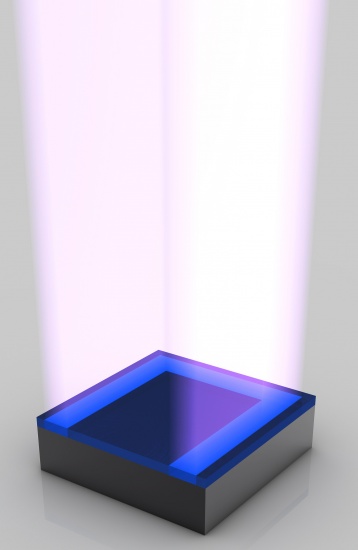

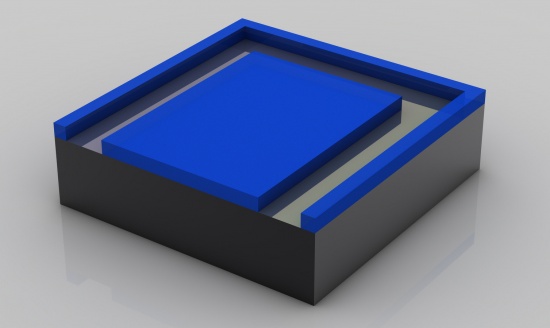

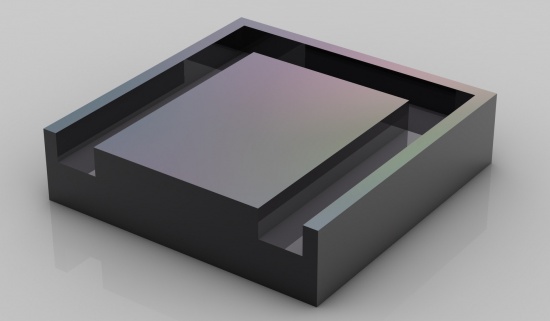

Vanaf de derde afbeelding zie je dit proces op transistorniveau: het masker zorgt ervoor dat het UV-licht op bepaalde wél op de fotolaag terecht komt en op andere plekken niet. Daarna wordt met een speciaal oplosmiddel de fotolaag verwijderd op de plekken waar het voor de UV-stralen zacht was geworden. Het resultaat zie je in de vierde afbeelding. De volgende stap is om met speciale chemicaliën stukken materiaal weg te etsen. De blauwe fotolaag is immuun tegen de stof die bij het etsen wordt gebruikt en beschermt zodoende de onderliggende gedeeltes. Op die manier vindt het etsen alleen plaats op de plekken waar de fotolaag eerder was weggehaald. Tenslotte wordt de fotolaag weggepoetst en krijg je het resultaat als in de onderste afbeelding.

Nogmaals: voor iedere laag die aan de chip wordt toegevoegd vindt dit hele proces plaats: eerst het materiaal over de hele chip plaatsen, fotogevoelige vloeistof toevoegen, maskeren met UV-licht, weg etsen op de plekken waar het materiaal niet hoor te zitten en daarna de fotolaag weer verwijderen.

Door de wafer te laten draaien wordt er een flinterdunne laag fotogevoelige vloeistof geplaatst.

Met behulp van een masker en UV-licht wordt de fotolaag op sommige plekken zachter gemaakt.

Zo ziet het maskeren met UV-licht er op transistor niveau uit.

Na het verwijderen van de vloeibaar gemaakte gedeeltes van de fotolaag is dit het resultaat.

Tijdens het etsen wordt er materiaal weggehaald. De resterende fotolaag bechermt onderliggende gedeeltes.

Het resultaat van lithografie en etsen.