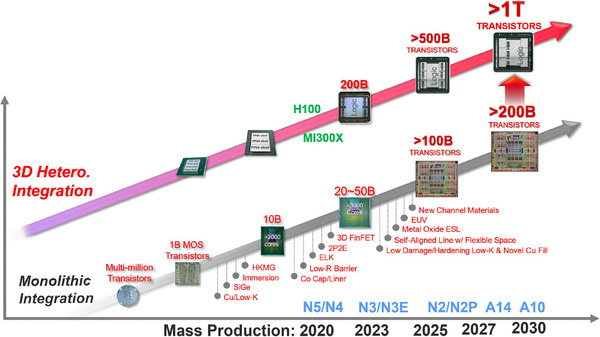

Tijdens de jaarlijkse IEEE International Electron Devices Meeting heeft TSMC een roadmap onthuld die weergeeft hoeveel transistors er op een enkele chip of package passen. Met behulp van geavanceerde procedés en 3D-stacking moet het naar eigen zeggen mogelijk zijn om tegen 2030 chips met 1 biljoen transistors te vervaardigen (op één package). Intel heeft een jaar geleden een soortgelijk doel bekendgemaakt.

Om deze mijlpaal te bereiken is de Taiwanese fabrikant volop bezig met zijn nieuwste productieprocessen. N2(P), A14 en A10 (1,4 en 1 nanometer) moeten allemaal tegen 2030 klaar zijn om chips op grote schaal te vervaardigen. Rond 2025-2026 worden de eerste monolithische chips met minstens 100 miljard transistors verwacht, gevolgd door 200 miljard tegen 2030. Ter referentie: de Nvidia RTX 4090, een van de grootste huidige consumentenchips, beschikt over 76,3 miljard transistors.

De vooruitgang van procestechnologie op zich volstaat echter niet meer om vooruitgang te blijven boeken. Zo zet TSMC ook volop in op geavanceerde packagingtechnieken om meerdere chiplets op één package te plaatsen. De fabrikant neemt momenteel onder meer de productie van Nvidia’s H100- en H200-accelerators voor zijn rekening, waarbij één grote compute-die wordt gecombineerd met meerdere stacks hbm-geheugen. AMD’s MI300X bestaat uit niet minder dan 13 chiplets, waarbij verschillende gpu- en cpu-chips worden gecombineerd met hbm.

Bron: Tom's Hardware