Een kwestie van timing

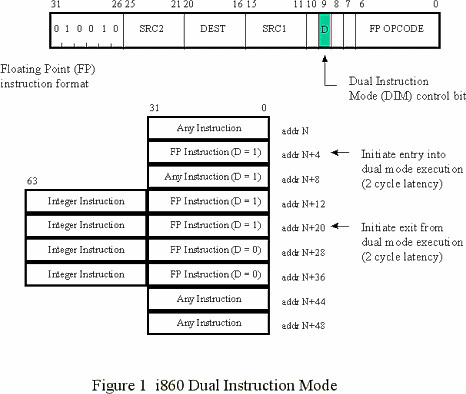

Het meest unieke architectonische kenmerk van de i860 is misschien wel het parallellisme op de chip. De twee 32bit-segmenten van de instructiecache voorzien in twee gelijktijdige 32bit-instructies: de ene aan de RISC-kern en de andere aan het floating-pointgedeelte. Nog een stap verder doen bepaalde floating-point instructies tegelijkertijd een beroep op de adder en de vermenigvuldiger. Het resultaat is een totaal van drie bewerkingen die in één klokcyclus worden uitgevoerd.

Deze architectuur verhoogt de snelheid van de chip, maar omdat hij de timing bemoeilijkt, levert de toepassing ervan problemen op. Indien bijvoorbeeld twee of drie parallelle bewerkingen dezelfde gegevens opvragen, moeten zij serieel worden uitgevoerd. Veel bugs die in het ontwerp van de chip werden gevonden, hadden te maken met dit type synchronisatie.

De logica die een eenheid bevriest wanneer de benodigde gegevens even niet beschikbaar zijn, vormde echter een van de grootste problemen met de timing. Aanvankelijk dachten de ontwerpers dat deze situatie zich niet al te vaak zou voordoen, maar het parallellisme op de chip veroorzaakte dit vaker dan was verwacht. De bevriezingslogica groeide en groeide, totdat werd besloten hem opnieuw te ontwerpen.