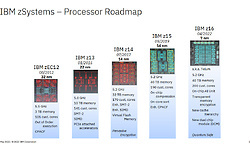

z16 met nieuwe Telum-processor

De nieuwste zSystem van IBM is de z16-mainframe. Er zijn twee versies; de A01 is het standaard IBM z-model en de LA1 is de LinuxONE Emperor 4-serveruitvoering. IBM heeft met deze generatie nieuwe toepassingen voor het mainframe aangesproken, op het gebied van kunstmatige intelligentie en quantumveilige encryptie.

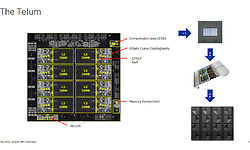

Om dit te bereiken, is er een nieuwe processor ontwikkeld, de Telum, met een bijzondere cache-lay-out. Bovendien is er een on-chip co-processor voor AI aanwezig, die realtime inference mogelijk moet maken. Dit betekent dat transacties tijdens de verwerking direct kunnen worden gecontroleerd aan de hand van AI-modellen. Zo kan een vermoedelijk frauduleuze transactie direct worden geblokkeerd. Dit is efficiënter dan controle achteraf, als de transactie al voltooid is.

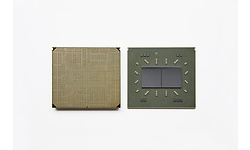

5,2GHz op 7nm

De Telum bevat 2,2 miljard transistors op 530 vierkante millimeter en wordt door Samsung geproduceerd op een 7nm-node. Elke die bestaat uit zeventien lagen en bevat meer dan dertig kilometer aan metaaldraad. De acht cores en zestien threads halen een kloksnelheid van 5,2 gigahertz, goed voor een per-socket prestatieverbetering van 40 procent ten opzichte van de z15. Elk central processorcomplex bestaat uit vier sockets in een lade, waarvan er vier per systeem kunnen worden gebruikt. De dualchip-modules bevatten twee dies per package, voor een maximum van vier maal acht processors per systeem. In totaal zijn er tweehonderd cores beschikbaar voor virtualisatie, van de 256 fysieke rekenkernen die maximaal aanwezig kunnen zijn.

Superscalar-architectuur

De z/Architecture-processors zijn zogenaamde superscalar processors, wat erop duidt dat meerdere instructies tegelijk worden ingeladen. De volgorde van uitvoering kan worden aangepast, afhankelijk van de instructies, en wordt bepaald door de verschillende pipelines. Er kunnen zes instructies worden gedecodeerd per klokcyclus, en maximaal tien instructies kunnen tegelijk worden uitgevoerd. Er is ondersteuning voor geheugenadressen van 24, 31 en 64 bit naast elkaar, waardoor ook oudere software kan worden gebruikt.

Complexe cache-lay-out

Elke core beschikt over 256 kilobyte Level 1-cache, waarvan de helft voor instructies en de andere helft voor data. Er is 32 megabyte Level 2-cache met een latency van 3,8 nanoseconden, die net als de L1 is uitgevoerd als fysieke static random access memory, oftewel sram. Dit geheugen is onderling verbonden middels een ring met een bandbreedte van 320 gigabyte per seconde, die per chip als 256MB L3-cache functioneert met een latency van gemiddeld 12 nanoseconden.

De vier dualchip-modules binnen een processorlade kunnen ook elkaars cache aanspreken, als virtuele L4-cache van 2GB per lade. Op elke chip kan data met een snelheid van 100GB/s in de ring worden geladen. De AI-accelerator is ook aan deze ring verbonden en kan intern data verplaatsen met een snelheid van maar liefst 600 GB/s .

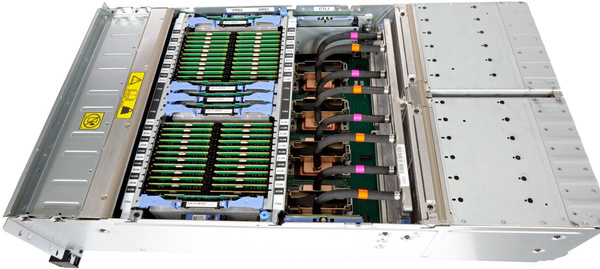

Gigantische geheugenconfiguratie

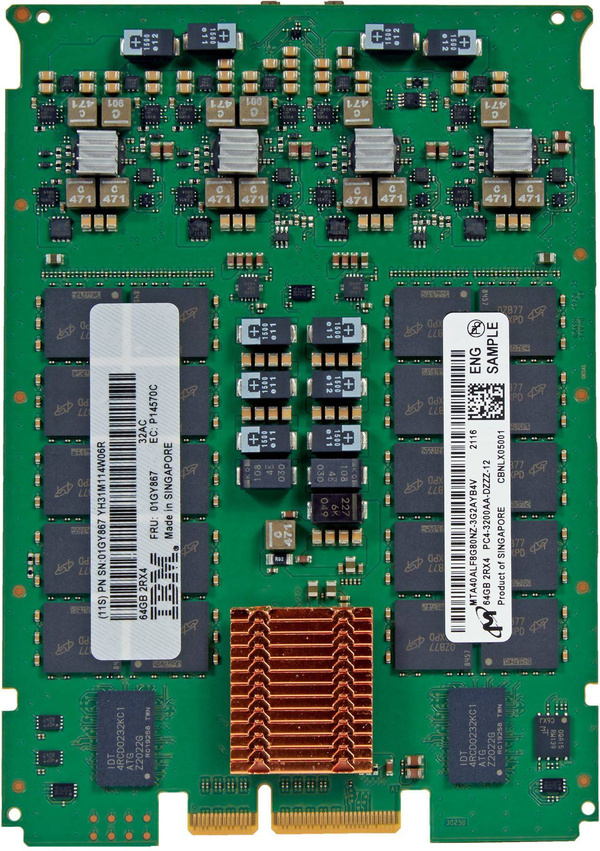

Het geheugen van maximaal 10TB per lade is verdeeld over 48 dimm's van 256 gigabyte, elk met hun eigen vrm's. Er zijn acht DDR4-3200-kanalen per processor beschikbaar. Bij het uitvallen van een module of kanaal zou geen data verloren moeten gaan en de workload zonder vertraging door kunnen gaan. Een eigen buffer-chip op elke module zorgt ervoor dat alle datastromen synchroon blijven. Foutcorrectie wordt uitgevoerd door de memory control unit op de processor.

Door het raim-ontwerp (redundant array of independent memory) is er meer ram geïnstalleerd dan gebruikt kan worden, zodat eventuele uitval kan worden opgevangen. Het falen van bits, lanes, dram-chips, DIMM's, sockets of complete geheugenkanalen kan worden gedetecteerd en gecorrigeerd door de mcu.

Elke processor krijgt een eigen stukje geheugen toegewezen, ter grootte van 8 kilobyte. Deze prefix storage area dient om interrupts of onderbrekingen te verwerken en eventuele fouten te corrigeren.

Vaste configuratie-opslag en virtueel flash-geheugen

De hardware system area of hsa van 256 gigabyte is gereserveerd voor verschillende interne functies, waarvan het grootste gedeelte voor css-functionaliteit. Hierdoor kunnen dynamisch logische partities (LPAR) worden aangemaakt in de zes logische channel subsystems. Hierbinnen zijn voor elke lcss vier subchannel sets, waaraan apparaten en crypto-adapters toegevoegd worden op maximaal 64.000 adressen. Doordat de huidige configuratie op elk moment is opgeslagen kan na volledige stroomuitval direct weer worden opgestart.

Virtual flash memory is een functie die als virtuele ssd-cache fungeert om wachttijden te verminderen en pieken in de belasting efficiënt te kunnen verwerken. Vfm kan in twaalf stappen van 512 gigabyte worden gebruikt; in totaal gaat het dus om zes terabyte.